Setting up the test, Creating an sopc builder testbench for the dut, Setting up the test –3 – Altera Avalon Verification IP Suite User Manual

Page 159: Creating an sopc builder testbench for the dut –3

Chapter 1: SOPC Builder Tutorial

1–3

Verifying Avalon-MM Slave DUT

May 2011

Altera Corporation

Avalon Verification IP Suite User Guide

Setting up the Test

This section describes the steps to build a test system in the SOPC Builder to verify the

on-chip RAM using the Avalon-MM Master BFM.

Creating an SOPC Builder Testbench for the DUT

Before you run the design file, unzip the ug_avalon_verification.zip file to a working

directory on your hard drive. This location is referred to as

To create an SOPC Builder testbench, follow these steps:

1. On the Windows Start menu, point to All Programs, then Altera, and click

Quartus II>

2. Open the master_bfm_project.qpf file located in

3. On the Tools menu, click SOPC Builder to launch the SOPC Builder tool.

4. Type “Avalon MM Master BFM” in the search field located in the Component

Library

panel. From the search results, double-click on the Avalon MM Master

BFM

component.

5. In the parameter editor, change the parameter values to match the values listed in

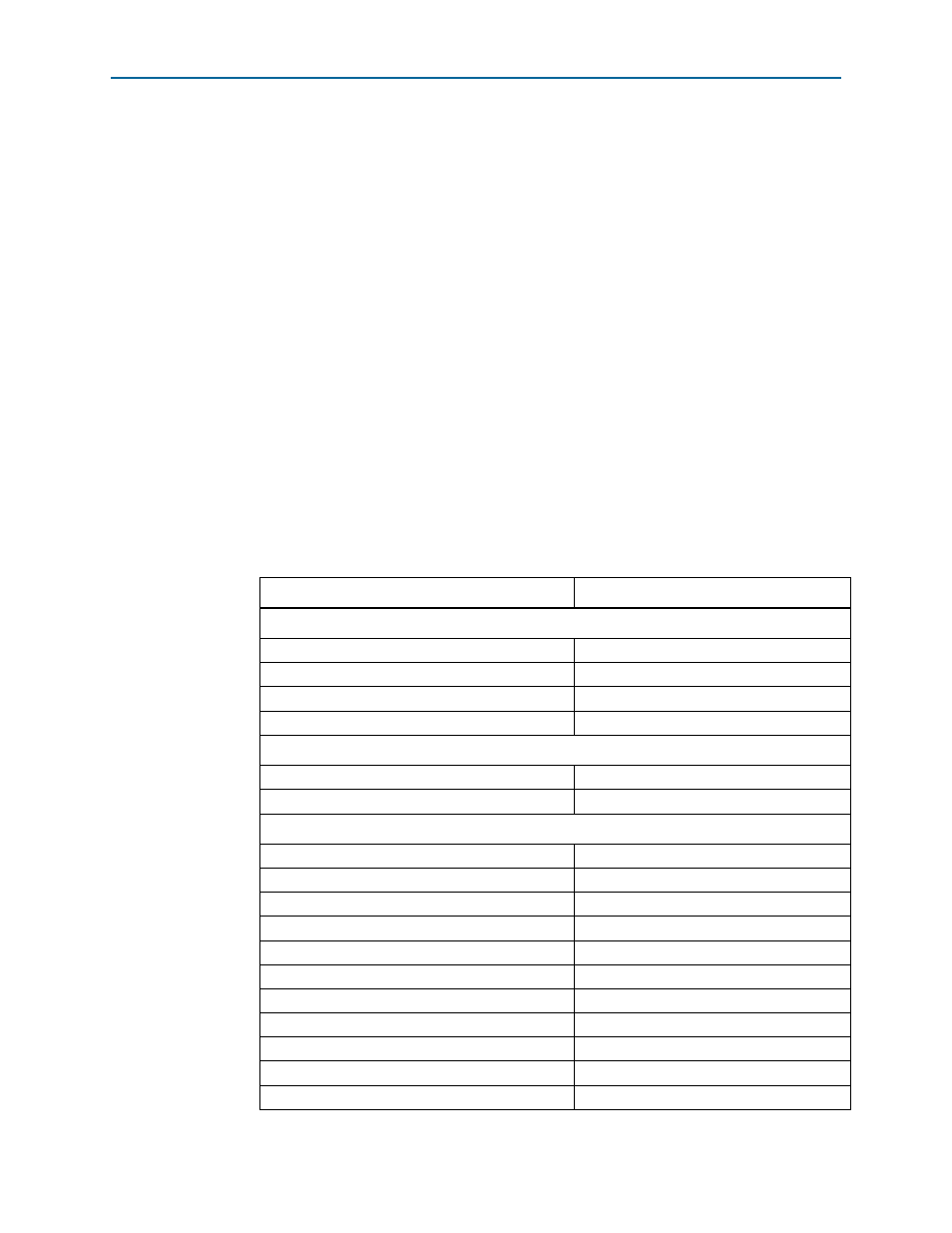

Table 1–1. Master BFM Parameter Values (Part 1 of 2)

Parameter

Value

Port Widths

Address width

16

Symbol width

8

Read Response width

8

Write Response width

8

Parameters

Number of symbols

4

Burstcount width

3

Port Enables

Use the read signal

On

Use the write signal

On

Use the address signal

On

Use the byteenable signal

On

Use the burstcount signal

Off

Use the readdata signal

On

Use the readdatavalid signal

On

Use the writedata signal

On

Use the begintransfer signal

Off

Use the beginbursttransfer signal

Off

Use the arbiterlock signal

Off