Application programming interface, Application example of bfms, Testbench – Altera Avalon Verification IP Suite User Manual

Page 15

I–2

Section I: Introduction to Avalon Verification IP Suite

Application Programming Interface

Avalon Verification IP Suite User Guide

May 2011

Altera Corporation

The Avalon Verification IP Suite also includes wrapper components so that the BFMs

can also be used in VHDL verification environments with simulators that support

mixed language simulation. These wrapper components are generated in SOPC

Builder only. Qsys does not support VHDL simulation with any BFMs other than the

Clock Source and Reset Source BFMs.

Application Programming Interface

Altera provides you with a set of application programming interface (API) for each

Avalon Verification IP Suite BFM that you can use to construct, instantiate, control,

and query signals in all BFM components. Your test programs must use only these

public access methods and events to communicate with each BFM.

1

While you can use methods other than the API, Altera does not guarantee continued

support or backwards compatibility of custom methods.

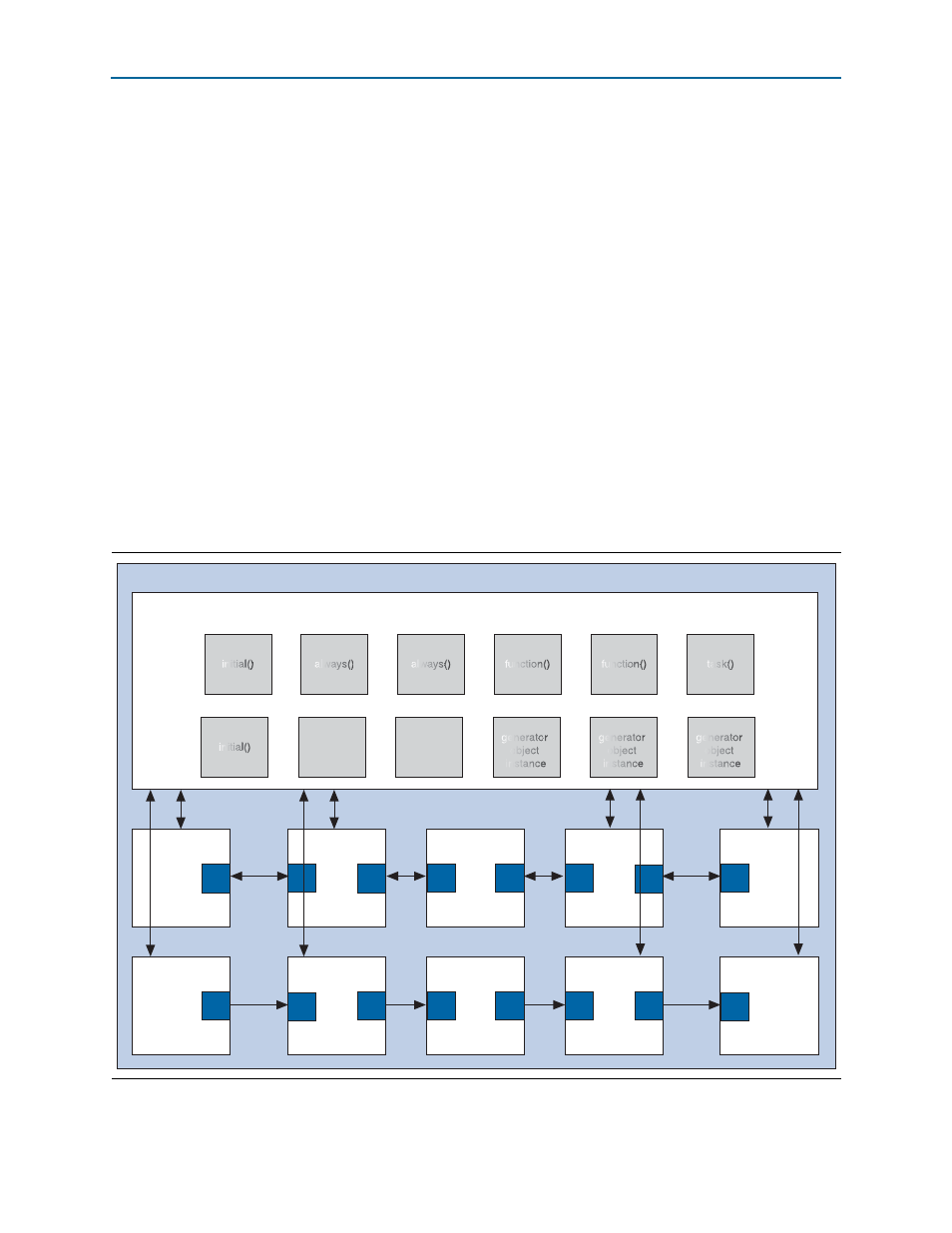

Application Example of BFMs

shows the top-level blocks in a typical testbench to verify components with

Avalon-MM and Avalon-ST interfaces.

Figure 1–1. Avalon Verification IP Suite Testbench

Testbench

Test Program

Traditional Verilog Implementation

OR

Avalon-MM

read or

write

SystemVerilog with VM

configuration

SRC

Avalon-MM

read or

write

S

Avalon-MM

Slave BFM

S

Avalon-MM

Monitor

Avalon-MM

Master BFM

Avalon-MM

DUT

M

S

S

Avalon-MM

Monitor

Snk

Avalon-ST

Sink BFM

Snk

Avalon-ST

Monitor

Avalon-ST

Source BFM

Avalon-ST

DUT

Src

Src

Snk

Snk

Avalon-ST

Monitor

M

M

M

Src

Src

transactor

generator

object

instance

generator

object

instance

generator

object

instance

initial()

initial()

always()

always()

function()

function()

task()