Altera ALTDLL User Manual

Page 88

Chapter 4: Functional Description

4–52

Design Example: Implementing Half-Rate DDR2 Interface in Stratix III Devices

© February 2012

Altera Corporation

ALTDLL and ALTDQ_DQS Megafunctions User Guide

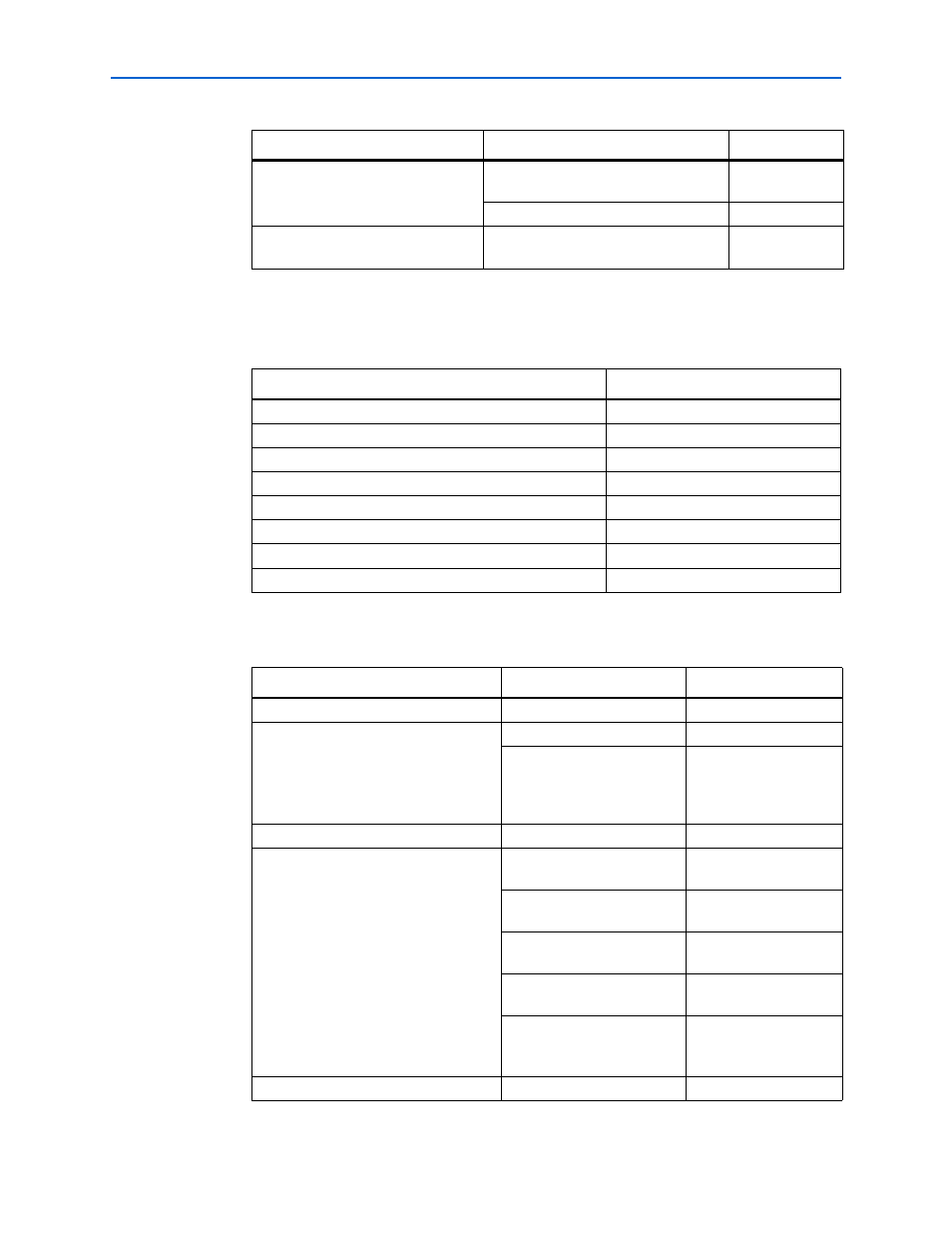

6. On the DQS OUT/OE page, specify the parameters as shown in

. These

parameters configure the DQS OUTPUT and DQS OE path of the ALTDQ_DQS

instance.

7. On the DQ IN page, specify the parameters as shown in

. These

parameters configure the DQ input path of the ALTDQ_DQS instance.

Advanced enable control options

DQS Enable Control Phase setting

Set Statically to

‘0’

DQS Enable Control Invert Phase

Never

Enable DQS enable block delay

chain

—

Turned on

Table 4–28. Advance Options (DQS OUT/OE)

Parameter

Value

Enable DQS Output Path

Turned on

Enable DQS output delay chain1

Turned on

Enable DQS output delay chain2

Turned on

]DQS output register mode

DDIO

Enable DQS output enable

Turned on

Enable DQS output enable delay chain1

Turned on

Enable DQS output enable delay chain2

Turned on

DQS output enable register mode

DDIO

Table 4–29. Advance Options (DQ IN) (Part 1 of 2)

Parameter

Sub-options

Value

DQ input register mode

—

DDIO

DQ Input Register Options

DQ input register clock source

—

‘dqs_bus_out’ port

—

Turned off Connect

DDIO clkn to DQS_BUS

from complementary

DQSn

Use DQ input phase alignment

—

Turned on

Advanced DQ IPA Options

DQ Input Phase Alignment

Phase Setting

Set statically to ‘0’

Add DQ Input Phase

Alignment Input Cycle Delay

Never

Invert DQ Input Phase

Alignment Phase

Never

Register DQ input phase

alignment bypass output

Turned on

Register DQ input phase

alignment add phase

transfer

Turned off

Use DQ resync register

—

Turned off

Table 4–27. Advanced Options (DQS IN) (Part 2 of 2)

Parameter

Sub-options

Value