Altera ALTDLL User Manual

Page 34

3–16

Chapter 3: Parameter Settings

ALTDQ_DQS Parameter Editor

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

describes the options available on the OCT Path page. This

page allows you to configure the DQ and DQS OCT paths. For more information

about the DQ and DQS OCT paths, refer to

“DQ/DQS OCT Path” on page 4–14

.

Create

‘io_clock_divider

_slaveout’ output

port

—

USE_IO_CLOCK_

DIVIDER_SLAVEOUT

Enables the output of the divider’s D flip-flop (DFF). The

output signal can only be connected to the

masterin

input of another I/O clock divider block and it cannot

have more than one fan-out. Turn on this parameter

when you chain the I/O clock divider blocks from

multiple ALTDQ_DQS instances.

IO Clock Divider

Invert Phase

Always,

Never, or

Based on

register

configuration

IO_CLOCK_DIVIDER_

INVERT_PHASE

If you turn on Always, the phase output is inverted. If

you turn on Never, the phase output is not inverted. If

you turn on Based on register configuration, the

phaseinvertctrl

input determines whether or not

the inverter is used. The inverter can be used to increase

the number of available phases.

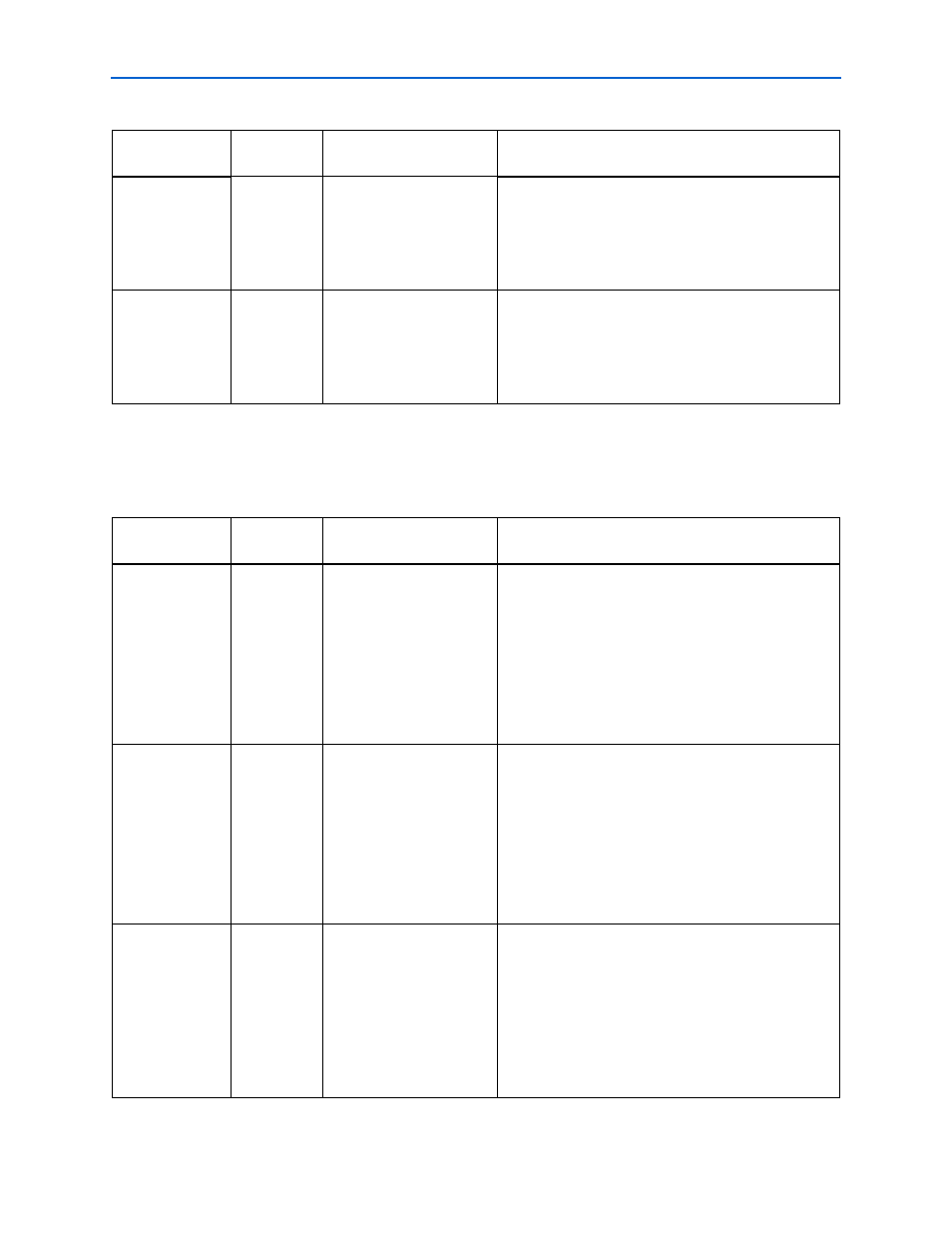

Table 3–8. Options on Half-Rate Page (Part 2 of 2)

Parameter Name

Legal Value

Clear Box

Parameter Name

Description

Table 3–9. Options on OCT Path Page

Parameter Name

Legal Value

Clear Box

Parameter Name

Description

Dynamic

Termination

Control Options

Enable Dynamic

Delay-chain1

—

USE_OCT_DELAY_

CHAIN1

Enables

_OCT_DELAY_CHAIN1

(D5) on both the

DQ and DQS dynamic OCT paths. The external memory

interfaces synchronize the timing of the turning on and

off of the parallel termination during reads and writes

from both the DQ and DQS pins, and to improve overall

timing margins.

D5 is a run-time adjustable delay chain.

For more information about configuring delay chains

dynamically, refer to

.

Dynamic

Termination

Control Options

Enable Dynamic

Delay-chain2

—

USE_OCT_DELAY_

CHAIN2

Enables

_OCT_DELAY_CHAIN2

(D6) on both the

DQ and DQS dynamic OCT paths. The external memory

interfaces synchronize the timing of turning on and off of

the parallel termination during reads and writes from

both the DQ and DQS pins, and to improve overall timing

margins.

D6 is a run-time adjustable delay chain.

For more information about configuring delay chains

dynamically, refer to

.

OCT register

mode

Not used, FF,

or DDIO

OCT_REG_MODE

Enables the full-rate dynamic OCT registers

(

_OCT_FF

or

_OCT_DDIO

registers) on

both the DQ and DQS dynamic OCT paths. Select FF if

you want flip-flop registers or DDIO if you want double

data rate I/O registers.

For more component information about this block, refer

to the “Dynamic On-Chip Termination Control” section in

the External Memory Interface chapter of the respective

device handbooks.