Altera ALTDLL User Manual

Page 110

A–9

Clear Box Generator Options

© February 2012

Altera Corporation

ALTDLL and ALTDQ_DQS Megafunctions User Guide

summarizes the Clear Box parameters for the ALTDQ_DQS megafunction

to configure the DQS output path.

IO_CLOCK_DIVIDER_INVERT_

PHASE

Optional

FALSE

FALSE, TRUE,

DYNAMIC

If set to

TRUE

, the phase output is

inverted. If set to

FALSE

, the phase

output is not inverted. If it is set to

DYNAMIC

, the

phaseinvertctrl

input determines whether the inverter

is used or not. Use the inverter to

increase the number of available

phases.

USE_IO_CLOCK_DIVIDER_

MASTERIN

Optional

FALSE

FALSE, TRUE

If set to

TRUE

, then the masterin input

is used to synchronize this divider with

another

IO_CLOCK_DIVIDER

. If set

to

FALSE

, this divider operates

independently (this mode is meant for

the master divider for a group of

dividers).

IO_CLOCK_DIVIDER_CLK_

SOURCE

Optional

Core

Core, dqs_bus,

inverted_dqs_bus

If

Core

,

IO_CLOCK_DIVIDER:clk

port on

the primitive is fed by

io_clock_divider_clk

port on

the megafunction.

If

dqs_bus

,

IO_CLOCK_DIVIDER:clk

port on

the primitive is fed by

dqs_bus_out

port on the megafunction.

If

inverted_dqs_bus

,

IO_CLOCK_DIVIDER:clk

port on

the primitive is fed

by

!dqs_bus_out

port on the

megafunction.

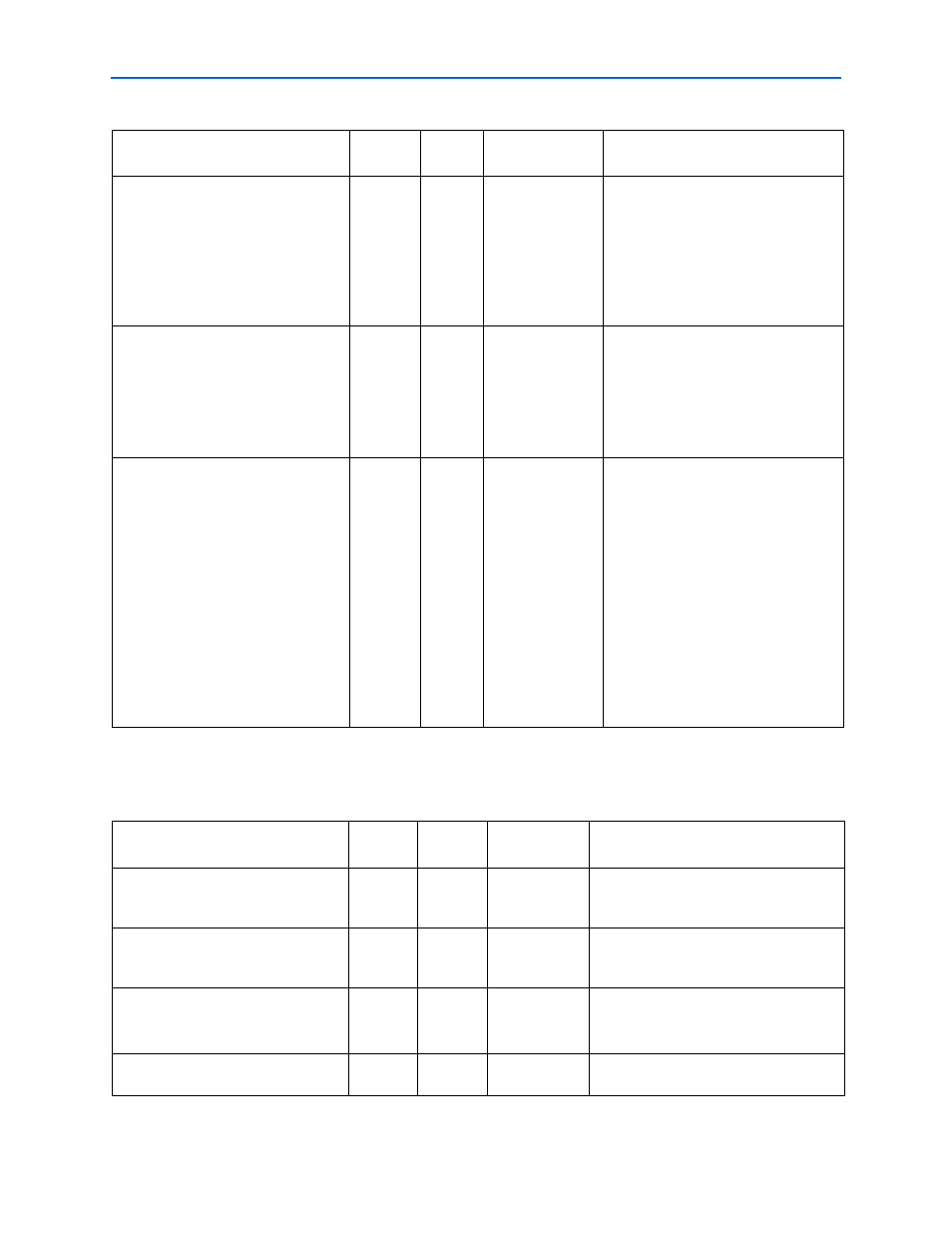

Table A–3. Megafunction Parameters to Configure DQS Input Path

(Part 4 of 4)

Parameter Name

Optional/

Required

Default

Legal Values

Description

Table A–4. Megafunction Parameters to Configure DQS Output Path

(Part 1 of 2)

Parameter Name

Optional/

Required

Default

Legal Values

Description

USE_DQS_OUTPUT_DELAY_

CHAIN1

Optional

FALSE

FALSE, TRUE

Instantiates

DQS_OUTPUT_DELAY_CHAIN1

if

TRUE

.

USE_DQS_OUTPUT_DELAY_

CHAIN2

Optional

FALSE

FALSE, TRUE

Instantiates

DQS_OUTPUT_DELAY_CHAIN2

if

TRUE

.

DQS_OUTPUT_REG_MODE

Optional

NONE

NONE, FF,

DDIO

Instantiates

DQS_OUTPUT_FF

if

FF

.

Instantiates

DQS_OUTPUT_DDIO_OUT

if

DDIO

.

DQS_OUTPUT_REG_POWER_

UP

Optional

LOW

LOW, HIGH

This parameter describes the power-up

condition of all registers in the primitive.