Altera ALTDLL User Manual

Page 20

3–2

Chapter 3: Parameter Settings

ALTDLL Parameter Editor

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

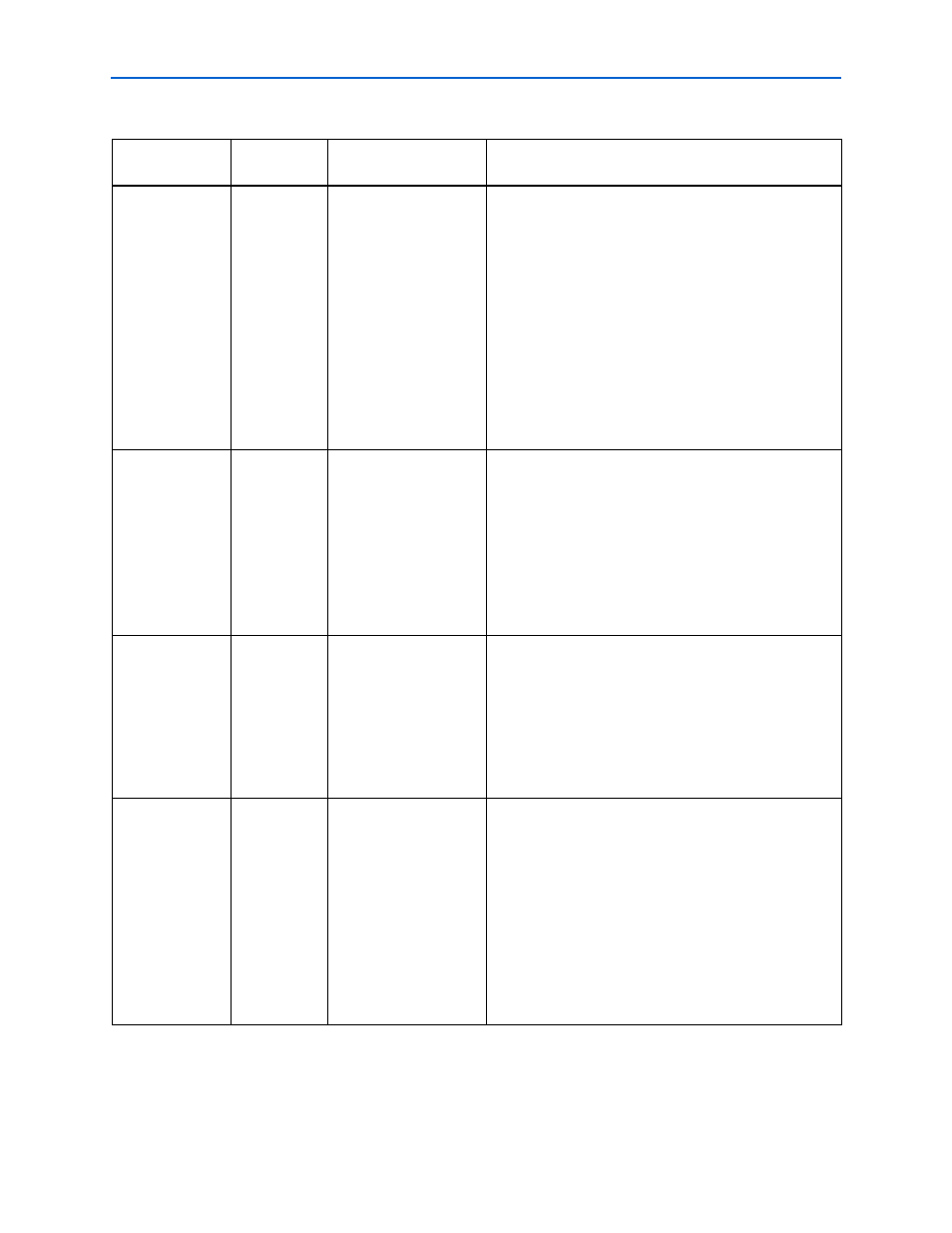

Table 3–1. Options on General Settings Page

Parameter Name

Legal Value

Clear Box

Parameter Name

Description

Number of Delay

Chains

6, 8, 10, 12,

or 16

DELAY_CHAIN_

LENGTH

Represents the number of delay buffers in the delay loop.

The DLL consists of 6, 8, 10, 12, or 16 DLL-controlled

delay buffers chained together. The total delay in the DLL

delay chain is computed with the following equation:

delay = delay_chain_length x delay_buffer_delay

The DLL uses the delay chain to implement a 360° phase

shift. By comparing the incoming clock to the 360°-shifted

clock, the DLL determines the delay setting to implement

an actual 360° phase shift in its delay chain. Because each

delay buffer is identical, each buffer in the delay chain

implements a phase shift that is equal to

(360/delay_chain_length)°.

The default value is 12.

DQS Delay Buffer

Mode

Low or High

DELAY_BUFFER_

MODE

Specifies the frequency mode for the variable delay

buffers.

If you select Low, the

dll_offset_ctrl_a_offsetctrlout [5..0]

or

dll_offset_ctrl_b_offsetctrlout

[5..0]

output is limited to a maximum value of 63.

If you select High, the output is limited to a maximum value

of 31.

The default value is Low.

Input Clock

Frequency

INPUT_FREQUENCY

Specifies the frequency of the clock (in MHz) that is

connected to the

clk

input port. This frequency must be

within the valid range for the device you are using. You can

specify a duration in ps. The value is in floating-point

format with no decimal point limit.

The default value is 300 MHz.

For information about the clock range for the Altera

devices, refer to the respective device handbook.

Turn on jitter

reduction

—

JITTER_REDUCTION

Enables the jitter reduction circuit. Jitter affects the signal

integrity of the clock signal from a PLL clock source or an

external clock pin. If you turn on this parameter, the jitter

reduction circuit is enabled on the

dll_delayctrlout[5..0]

and

dll_offset_ctrl_a_offsetctrlout [5..0]

,

or the

dll_offset_ctrl_b_offsetctrlout

[5..0]

output port.

When the jitter reduction circuit is enabled, the DLL may

require up to 1,024 clock cycles to lock. When the jitter

reduction circuit is disabled, the DLL requires only up to

256 clock cycles to lock.