Getting started, Design flow, Build the datapath – Altera ALTDLL User Manual

Page 7: Chapter 2. getting started, Design flow –1, Build the datapath –1

© February 2012

Altera Corporation

ALTDLL and ALTDQ_DQS Megafunctions User Guide

2. Getting Started

Design Flow

This chapter describes the FPGA design flow to implement a custom memory

interface datapath using the ALTDLL and ALTDQ_DQS megafunctions and Altera’s

FPGA hardware features.

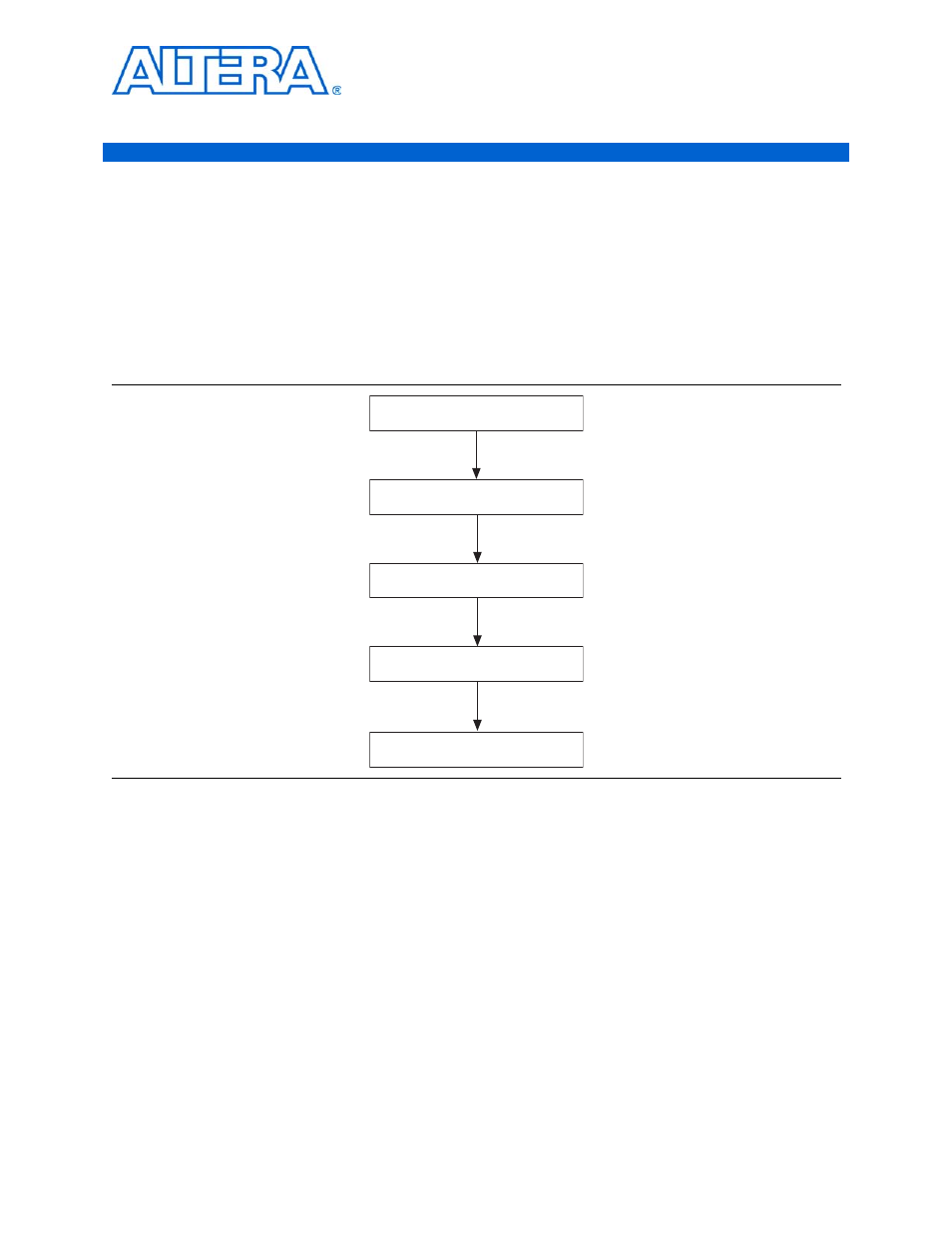

shows the design flow for creating a custom memory datapath system

with the ALTDLL and ALTDQ_DQS megafunctions and the Quartus

®

II software.

Build the Datapath

After you identify the requirements for your custom external memory interface, the

first stage is to build a datapath to interface with the memory blocks.

To build the datapath, you must perform the following steps:

1. Create a project in the Quartus II software that targets the preferred Altera device.

2. Instantiate the ALTPLL megafunction to provide the required clocking scheme for

the custom PHY.

f

For more information about instantiating megafunctions and the clocking

scheme, refer to Instantiate the ALTPLL Megafunction section in

of

the External Memory Interface Handbook. For more information about using

PLLs, refer to the

3. Instantiate the ALTDLL megafunction to implement the DLL.

Figure 2–1. Design Flowchart

Build the Datapath

Simulate the Design

Create Timing Constraints

Compile the Design and Verify Timing

Adjust Constraints