Generate the megafunctions, Generate the megafunctions –5 – Altera ALTDLL User Manual

Page 11

2–5

Chapter 2: Getting Started

Design Example: Implementing Read Paths Using Stratix III Devices

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

Generate the Megafunctions

Create a Quartus II project and generate the following megafunctions:

■

ALTPLL megafunction

■

ALTDLL megafunction

■

ALTDQ_DQS megafunction

■

ALTIOBUF megafunction

Create a Quartus II Project

Create a project in the Quartus II software that targets the EP3SL150F1152-C2 device

for the DDR2 SDRAM by performing the following steps:

1. Open the altdll_altdq_dqs_DesignExample_ex1.zip file and extract the

altdll_altdq_dqs_design_ex1.qar

file.

2. In the Quartus II software, restore the altdll_altdq_dqs_design_ex1.qar file into

your working directory.

3. Open the altdll_altdq_dqs_design_ex1.bdf file.

Generate the ALTPLL Megafunction

Before generating the ALTDLL and ALTDQ_DQS megafunctions, you must generate

the ALTPLL megafunction first by performing the following steps:

1. Double-click anywhere on the Block Editor window. The Symbol window appears.

2. Click MegaWizard Plug-In Manager. Page 1 of the MegaWizard

™

Plug-In

Manager appears.

3. Select Create a new custom megafunction variation.

4. Click Next. Page 2a of the MegaWizard Plug-In Manager appears.

5. Select Create a new custom megafunction variation.

6. Click Next. Page 2a of the MegaWizard Plug-In Manager appears. Select ALTPLL,

and Verilog HDL, and type the file name as PLL_50MHz.v.

7. On the Parameter Settings tab, on the General/Modes page, specify the

. These parameters configure the general

settings for the ALTPLL instance.

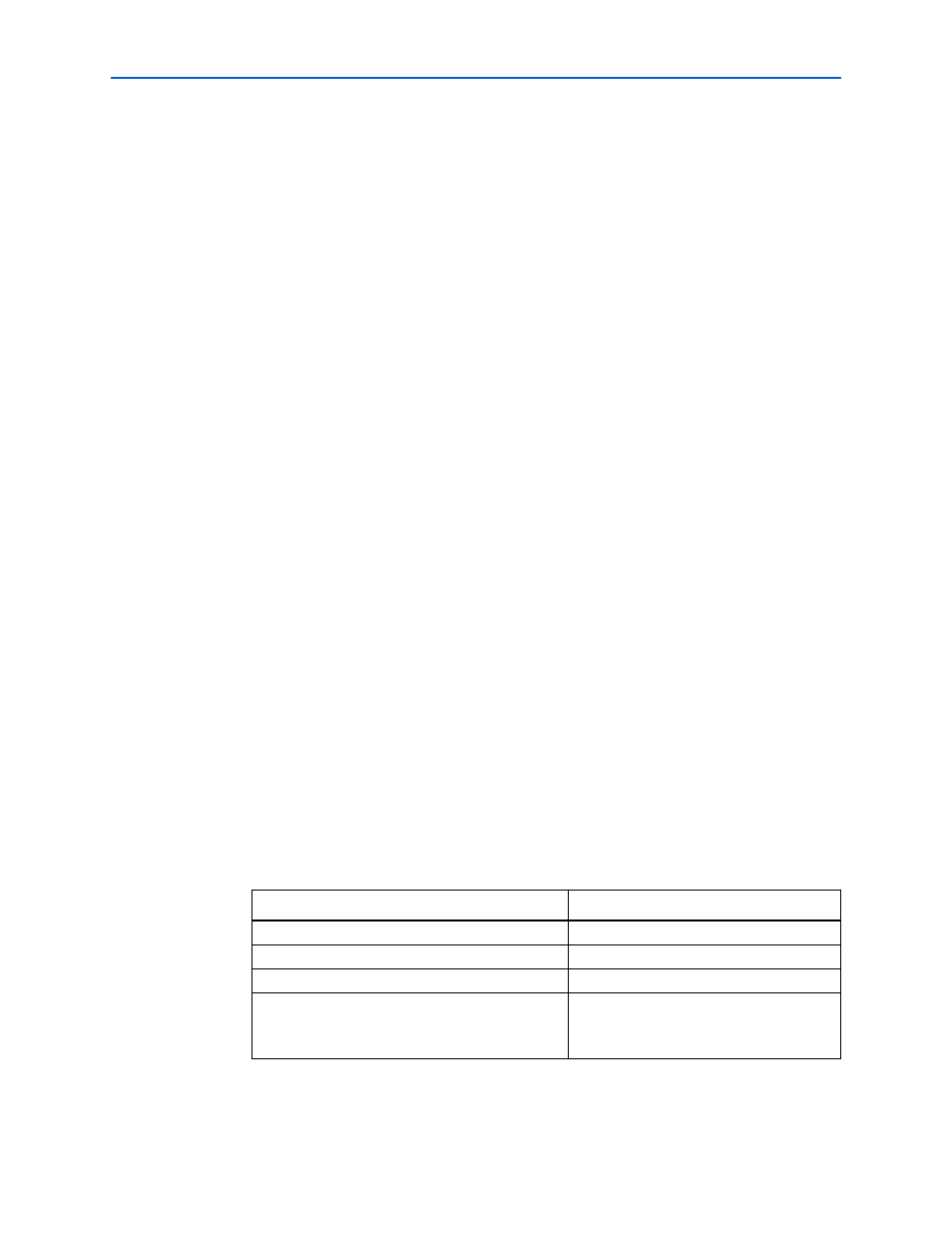

Table 2–1. ALTPLL Parameter Settings

Settings

Value

Currently selected device family

Stratix III

Match project/default

Turned on.

What is the frequency of the inclock0 input?

50 MHz

How will the PLL outputs be generated?

With no compensation

This option is selected because the PLL is

used to clock the ALTDLL instance only.