Procedure, Procedure –49 – Altera ALTDLL User Manual

Page 85

4–49

Chapter 4: Functional Description

Design Example: Implementing Half-Rate DDR2 Interface in Stratix III

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

Design Example: Implementing Half-Rate DDR2 Interface in Stratix III

Devices

This section describes a design example that uses the DLL and DQ/DQS circuitry

with half-rate DDR2 external memory interface in Stratix III devices. The memory

interface is running at 333.333 MHz with 8-bit bidirectional DQ pins, a 1-bit output

DQ pin, and a 1-bit differential DQS pin.

f

The design examples are available next to the ALTDLL and ALTDQ_DQS

Megafunction User Guides on th

page of the Altera

website.

Procedure

This example describes the following steps:

■

Instantiate the ALTDLL Megafunction

■

Instantiate the ALTDQ_DQS Megafunction

■

Instantiate the ALTIOBUF Megafunction

■

Instantiate the ALTDLL Megafunction

To instantiate the ALTDLL megafunction, perform the following steps:

1. Open the altdll_altdq_dqs_DesignExample_ex2.zip project and extract the

altdll_altdq_dqs_design_ex2.qar

file.

2. In the Quartus II software, open the altdll_altdq_dqs_design_ex2.qar file and

restore the archived file into your working directory.

3. On the Tools menu, click MegaWizard Plug-In Manager. Page 1 of the

MegaWizard Plug-In Manager appears.

4. Select Create a new custom megafunction variation.

5. Click Next. Page 2a of the MegaWizard Plug-In Manager appears. Select ALTDLL,

and Verilog HDL, and type the file name as dll_inst.v.

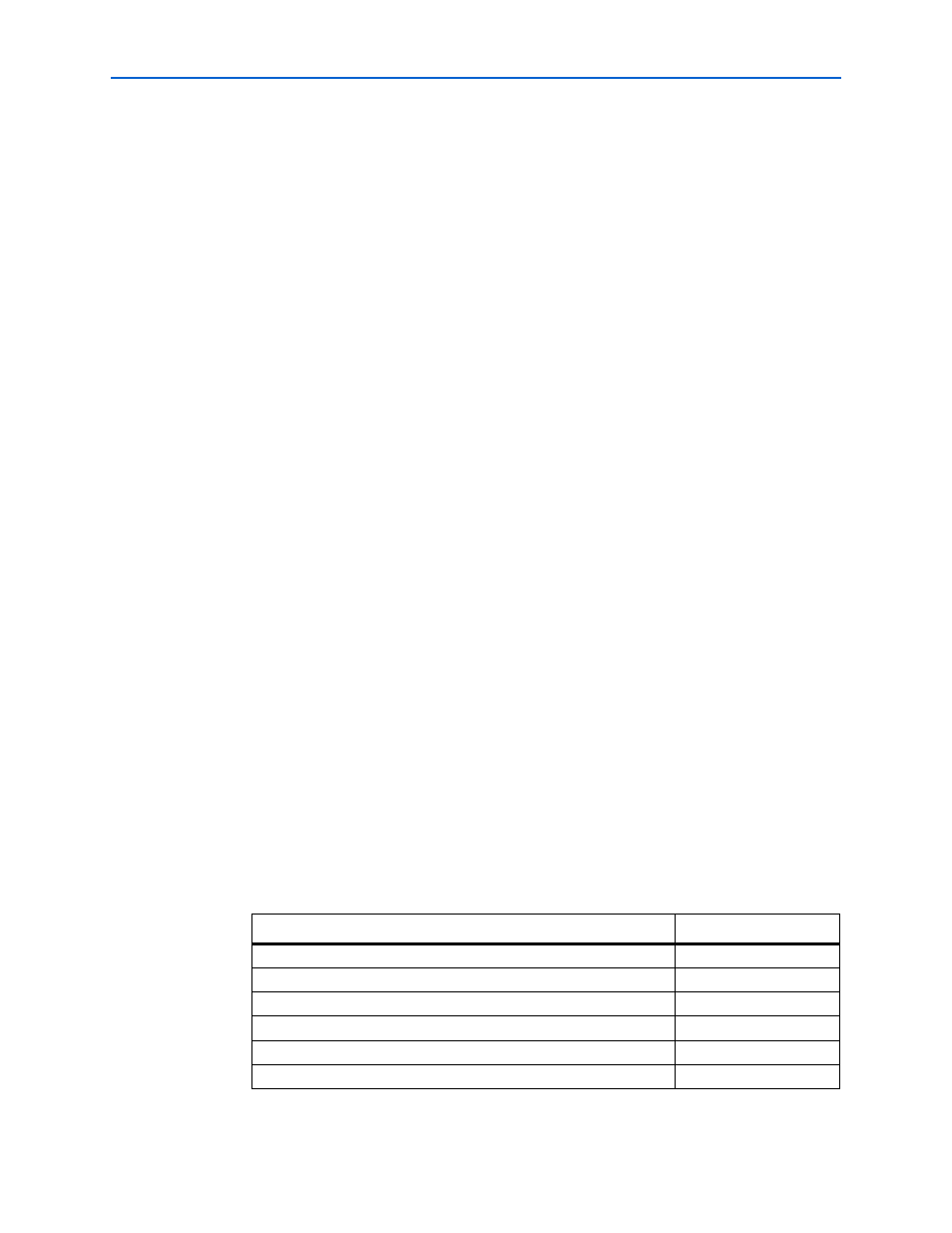

6. On the Parameter Settings tab, on the General page, specify the parameters as

shown in

. These parameters configure the general settings for the

ALTDLL instance.

Table 4–24. General Settings (Part 1 of 2)

Settings

Value

Currently selected device family

Stratix III

Match project/default

Turned on

Number of Delay Chains

10

DQS Delay Buffer Mode

High

Input Clock Frequency

333 MHz

Turn on jitter reduction

Turned off