Altera ALTDLL User Manual

Page 36

3–18

Chapter 3: Parameter Settings

ALTDQ_DQS Parameter Editor

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

The Simulation Model page allows you to optionally generate simulation model files.

The Summary page displays a list of the types of files to be generated. The

automatically generated variation file contains wrapper code in the language you

specified earlier. On this page, you can specify additional types of files to be

generated. Choose from the AHDL Include file (

component declaration file,

file (

page, the file for that netlist is also available. A gray checkmark indicates a file that is

automatically generated, and a red checkmark indicates generation of an optional file.

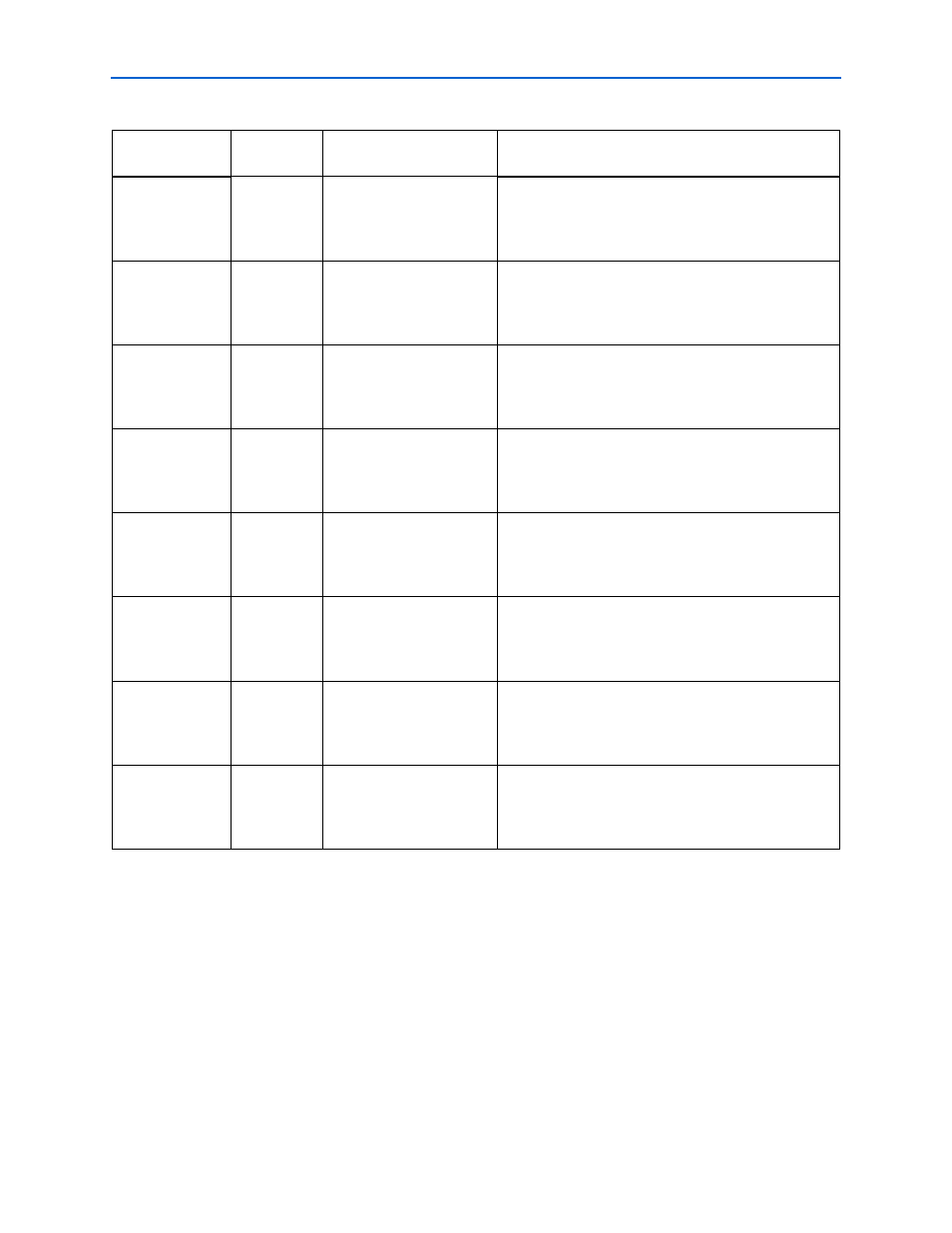

Reset ports

Create

'input_dq_sreset'

input port

—

—

Enables synchronous reset port that synchronously

resets all registers in the DQ input path.

Reset ports

Create

'output_dq_arese

t' input port

—

—

Enables asynchronous reset port that asynchronously

resets all registers in the DQ output or DQ OE path.

Reset ports

Create

'output_dq_srese

t' input port

—

—

Enables synchronous reset port synchronously resets all

registers in the DQ output or DQ OE path.

Reset ports

Create

'bidir_dq_areset'

input port

—

—

Enables asynchronous reset port that asynchronously

resets all registers in the bidirectional DQ I/O path.

Reset ports

Create

'bidir_dq_sreset'

input port

—

—

Enables synchronous reset port that synchronously

resets all registers in the bidirectional DQ I/O path.

Config ports

Create

'config_clk' input

port

—

—

Enables input clock port that feeds

IO_CONFIG

block

for user-driven dynamic delay chain. This input port is

used as the clock signal of the shift register block. The

maximum frequency for this clock is 30 MHz.

Config ports

Create

'config_datain'

input port

—

—

Enables input port that feeds the input data to the serial

load shift register in

IO_CONFIG

block for user-driven

dynamic delay chain.

Config ports

Create

'config_update'

input port

—

—

Enables input port that feeds

IO_CONFIG

block update

port for user-driven dynamic delay chain.

When asserted, the serial load shift register bits feed the

parallel load register.

Table 3–11. Options on Reset/Config Ports Page (Part 2 of 2)

Parameter Name

Legal Value

Clear Box

Parameter Name

Description