Altera ALTDLL User Manual

Page 33

Chapter 3: Parameter Settings

3–15

ALTDQ_DQS Parameter Editor

© February 2012

Altera Corporation

ALTDLL and ALTDQ_DQS Megafunctions User Guide

describes the options available on the Half-rate page.

DQ Output Enable

Options

Enable DQ output

enable delay

chain2

—

USE_DQ_OE_DELAY_

CHAIN2

Enables

_OE_DELAY_CHAIN2

(D6) in the DQ OE

path. This parameter is used for deskew purposes or

SSN reduction. D6 is a run-time adjustable delay chain.

For more information about configuring delay chains

dynamically, refer to

.

DQ Output Enable

Options

DQ output enable

register mode

Not used, FF,

or DDIO

DQ_OE_REG_MODE

Enables the full-rate DQ output-enable registers

(

_OE_FF

or

_OE_DDIO_OE

registers).

Select FF if you want flip-flop registers or DDIO if you

want double data rate I/O registers.

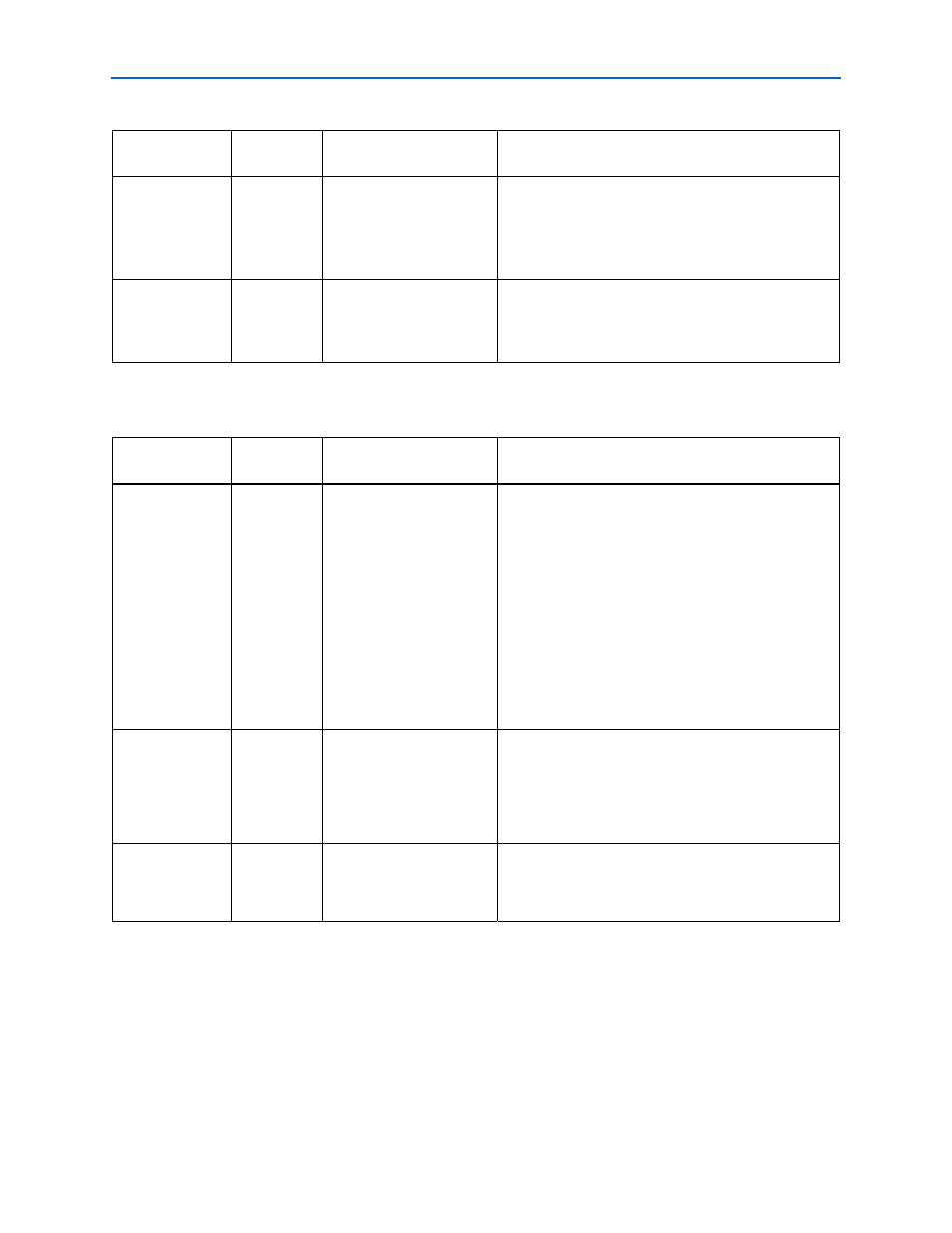

Table 3–7. Options on DQ OUT/OE Page (Part 2 of 2)

Parameter Name

Legal Value

Clear Box

Parameter Name

Description

Table 3–8. Options on Half-Rate Page (Part 1 of 2)

Parameter Name

Legal Value

Clear Box

Parameter Name

Description

IO Clock Divider

Source

Core,

‘dqs_bus_ou

t’ port, or

Inverted

‘dqs_bus_ou

t’ port

IO_CLOCK_DIVIDER_

CLK_SOURCE

Specifies the I/O clock divider clock source which can be

from the Core (FPGA), the ‘dqs_bus_out’ port (DQS

input path), or the Inverted ‘dqs_bus_out’ port (DQS

input path).

Altera recommends that you turn on the ‘dqs_bus_out’

port option to clock the DQ input register. When reading

from the external memory, the DQ data that comes from

the full-rate DQ input registers must be synchronized to

the half-rate input block, if half-rate interfaces are used.

If the full-rate DQ input registers are clocked by the DQS

input path via the

dqs_bus_out

port, then the I/O

clock divider (and other clock source settings) must also

be clocked via the

dqs_bus_out

port.

Create

‘io_clock_divider

_masterin’ input

port

—

USE_IO_CLOCK_

DIVIDER_MASTERIN

Enables the

masterin

input to synchronize this divider

with another I/O clock divider. If you turn off this option,

this divider operates independently. This mode is meant

for the master divider of a group of dividers. Turn on this

parameter when you chain the I/O clock divider blocks

from multiple ALTDQ_DQS instances.

Create

‘io_clock_divider

_clkout’ output

port

—

—

Divides the clock output signal by two. The clock out

signal can be connected to the clock input of a half-rate

Input block or fed to the FPGA core.