Altera ALTDLL User Manual

Page 30

3–12

Chapter 3: Parameter Settings

ALTDQ_DQS Parameter Editor

ALTDLL and ALTDQ_DQS Megafunctions User Guide

© February 2012

Altera Corporation

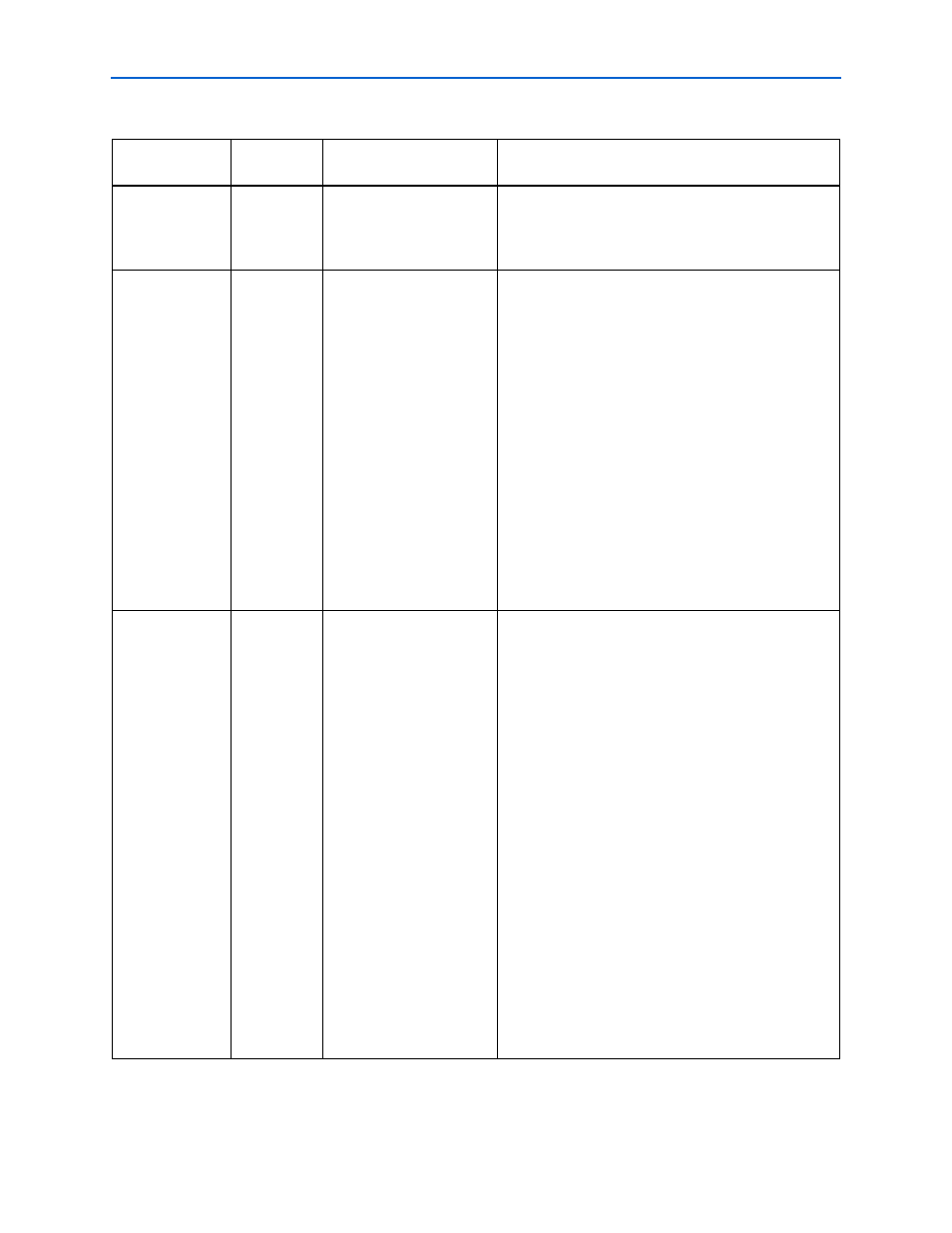

Table 3–6. Options on DQ IN Page

(Part 1 of 3)

Parameter Name

Legal Value

Clear Box

Parameter Name

Description

DQ Input Register

Options

DQ input register

mode

Not used, FF,

or DDIO

DQ_INPUT_REG_MODE

Enables the DQ input registers (

_INPUT_FF

or

_DDIO_IN

registers). Select FF if you want

flip-flop registers or DDIO if you want double data rate

I/O registers.

DQ Input Register

Options

DQ input register

clock source

‘dqs_bus_ou

t’ port,

Inverted

‘dqs_bus_ou

t’ port, or

Core

DQ_INPUT_REG_CLK_

SOURCE

Specifies how the DQ input registers should be clocked.

You can either clock it from the ‘dqs_bus_out’ port (DQS

input path), the Inverted ‘dqs_bus_out’ port (DQS input

path), or directly from the Core (FPGA).

Altera recommends that you turn on the ‘dqs_bus_out’

port option to clock the DQ input register. When reading

from the external memory, the DQ data that comes into

the DDIO must be center-aligned with the DQS strobe

that goes through the DQS input path and comes out the

dqs_bus_out

port. By center-aligning the DDIO with

DQS strobe, you maximize the setup and hold margins at

the DQ input register.

You can also connect the

dqs_bus_out

port to the

full-rate DQ input register for complementary clocking

purpose as used in QDR and QDR II applications. You

can connect the

dqs_bus_out

port by turning on the

Connect DDIO clkn to DQS_BUS from complementary

DQSn option.

DQ Input Register

Options

Use DQ input

phase alignment

—

USE_DQ_IPA

Enables the input phase alignment (

_IPA_LOW

or

_IPA_HIGH

) blocks. The input phase alignment

blocks represent the circuitry required to phase-shift the

input signal the DQ data for resynchronization and

alignment purpose. The resynchronization and alignment

are done to match the arrival delay of the DQS (triggered

by the fly-by clock on a DDR-DIMM) to the latest arrival

delay of a DQS from the DIMM.

Because this block is meant for resynchronization, the

ALTDQ_DQS megafunction does not consider the

clocking requirements of this block. You must figure the

clocking requirements using the RTD analysis or create a

custom data training circuitry to read or write back a

training pattern to and from the memory device, and

then dynamically adjust the PLL’s resyncronization clock

phase to find a good working phase.

For more component information about the available

alignment and resynchronization registers in this block,

refer to the “I/O Element (IOE) Registers” section in the

External Memory Interface chapter of the respective

device handbooks. For the available levelling delay

chains in this block, refer to the “Leveling Circuitry”

section in the External Memory Interface chapter of the

respective device handbooks.