Figure 4–26 on, Figure 4–26 – Altera ALTDLL User Manual

Page 101

4

–65

Ch

apt

er

4:

F

u

n

c

tiona

l

De

sc

rip

tio

n

De

sign Ex

ample: Implem

enting Ha

lf-

R

ate

DDR

2

Inter

face in

Stra

tix

III

AL

TD

LL

an

d

©

February 2012

Al

tera Cor

por

atio

n

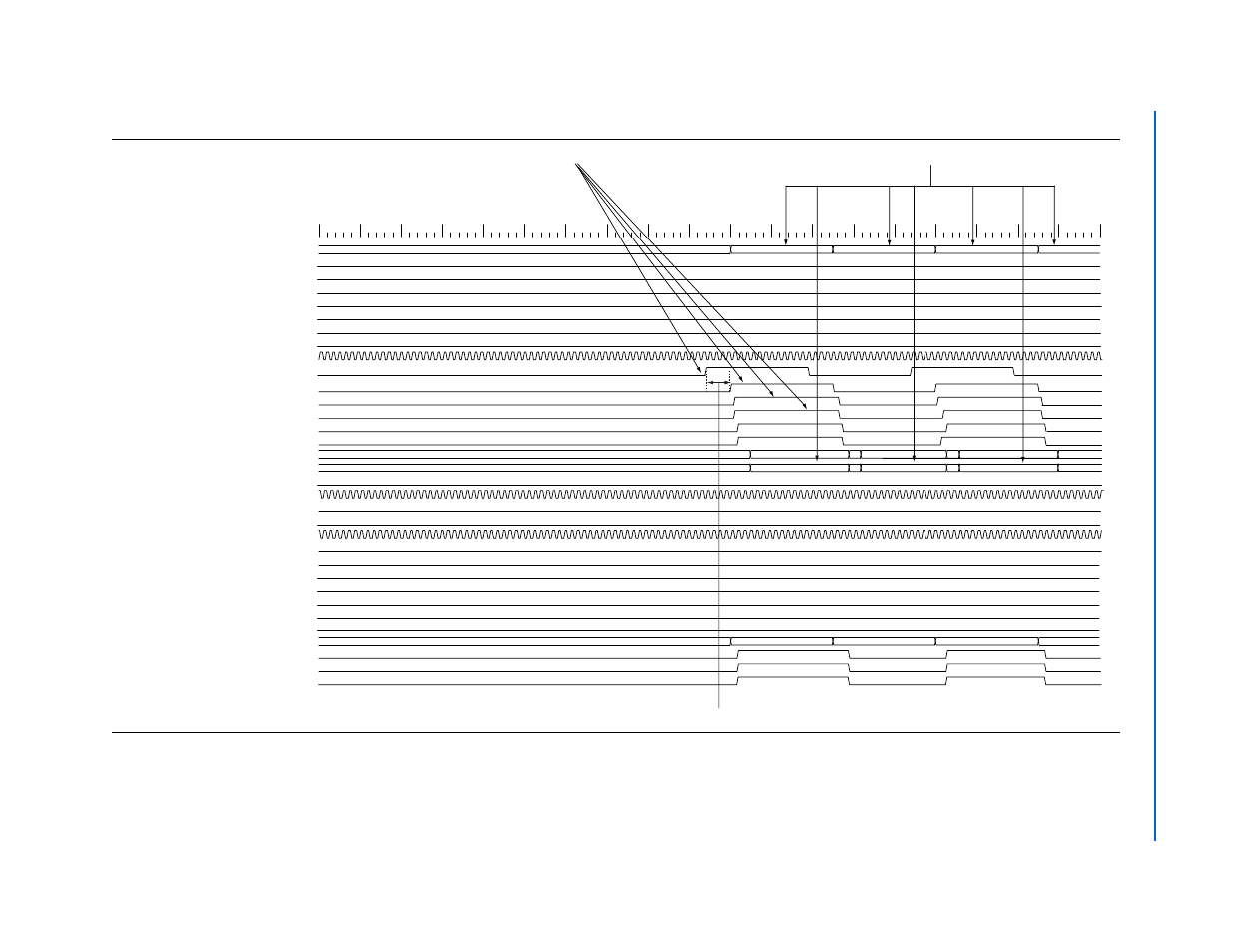

Figure 4–26. Data Transfer from the Bidirectional DQ Pin to the FPGA Core with 50-ps Delay Chain Activated

bidir_dq_0_input_delay_chain_inst.dataout

bidir_dq_0_ddio_in_inst.regouthi

bidir_dq_0_ddio_in_inst.regoutlo

bidir_dq_0_ipa_low_inst.dataout

bidir_dq_0_ipa_high_inst.dataout

bidir_dq_0_half_rate_input_inst.dataout[3:0]

bidir_dq_hr_input_data_out[31:0]

dqs_config_ena

c0

dqsn_io_config_ena

dqsn_hr_oe_in[1:0]

dqsn_io

dqs_io_config_ena

output_dq_io_config_ena

output_dq_hr_oe_in[1:0]

output_dq_0_oe_hr_ddio_out_inst.dataout

output_dq_0_oe_ddio_oe_inst.dataout

output_dq_0_oe_delay_chain1_inst.dataout

output_dq_0_oe_delay_chain2_inst.dataout

output_dq_hr_output_data_in[3:0]

output_dq_0_output_hr_ddio_out_high_inst.dataout

5.10us

5.12us

5.14us

5.16us

5.18us

5.20us

5.22us

5.24us

5.26us

5.28us

5.30us

5.32us

5.34us

5.36us

5.38us

5.40us

5.42us

5.44us

5.46us

bidir_dq_io[7:0]

dqs_hr_oe_in[1:0]

dqs_hr_output_data_in[3:0]

dqs_output_hr_ddio_out_low_inst.dataout

dqs_output_hr_ddio_out_high_inst.dataout

dqs_output_delay_chain1_inst.dataout

dqs_output_delay_chain2_inst.dataout

dqs_output_ddio_out_inst.dataout

dqs_io

FF

00

FF

F

3

0

8

F

FFFFFFFF

00000000

FFFFFFFF

F

0

F

output_dq_0_output_ddio_out_inst.dataout

output_dq_0_output_hr_ddio_out_low_inst.dataout

bidir_dq_0_input_delay_chain_inst.datain

[1]

[9]

[10]