Rainbow Electronics AT89C5122 User Manual

Page 51

51

AT8xC5122/23

4202E–SCR–06/06

Reset Value = X0X0 X000b

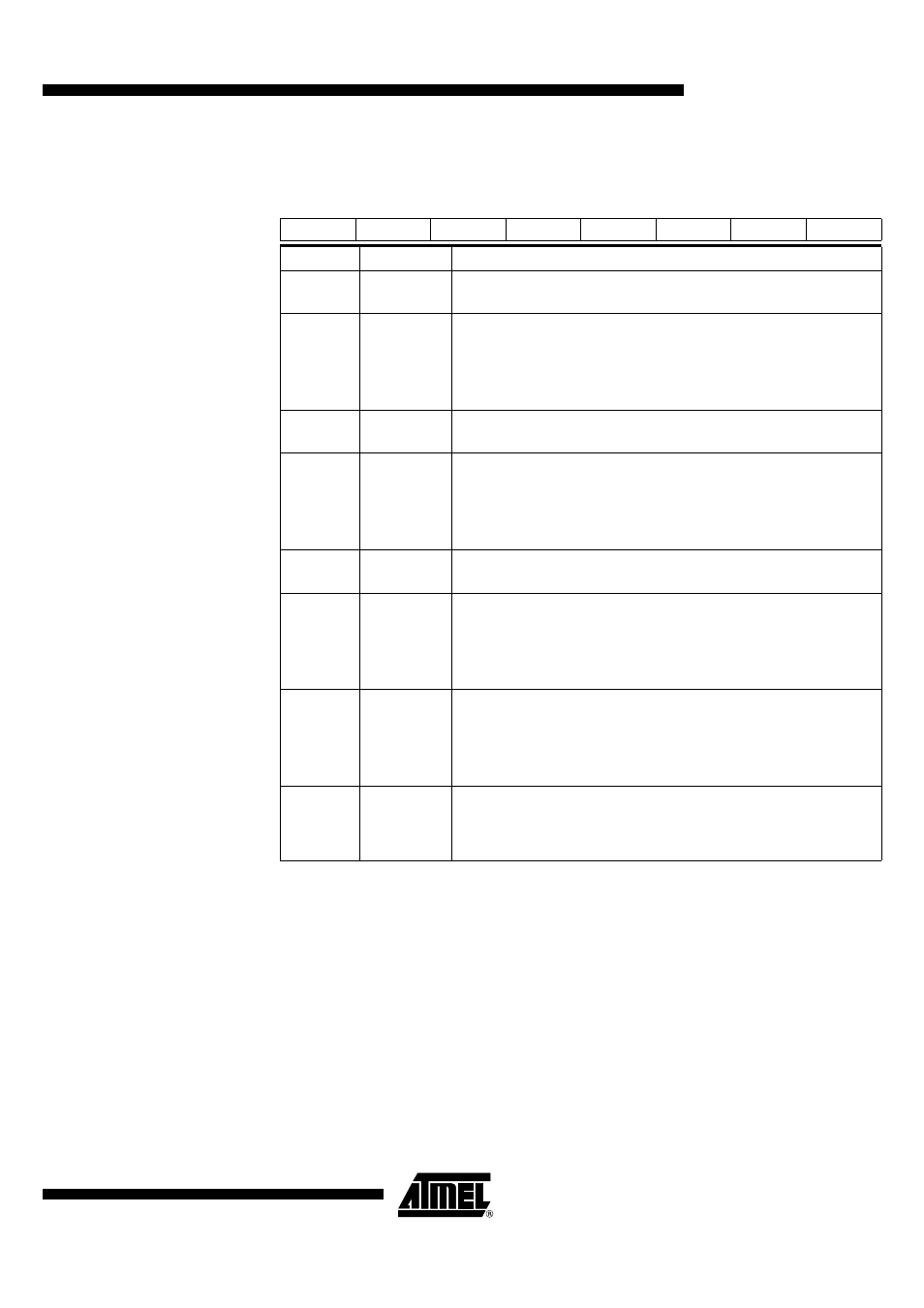

Table 26. Clock Configuration Register 0 - CKCON0 (S:8Fh)

7

6

5

4

3

2

1

0

-

WDX2

-

SIX2

-

T1X2

T0X2

X2

Bit Number Bit Mnemonic Description

7

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

6

WDX2

Watchdog clock

This control bit is validated when the CPU clock X2 is set; when X2 is low,

this bit has no effect.

Cleared to bypass the PR1 prescaler.

Set to select the PR1 output for this peripheral.

5

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

4

SIX2

Enhanced UART clock (Mode 0 and 2)

This control bit is validated when the CPU clock X2 is set; when X2 is low,

this bit has no effect.

Cleared to bypass the PR1 prescaler.

Set to select the PR1 output for this peripheral.

3

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

2

T1X2

Timer 1 clock

This control bit is validated when the CPU clock X2 is set; when X2 is low,

this bit has no effect.

Cleared to bypass the PR1 prescaler.

Set to select the PR1 output for this peripheral.

1

T0X2

Timer 0 clock

This control bit is validated when the CPU clock X2 is set; when X2 is low,

this bit has no effect.

Cleared to bypass the PR1 prescaler.

Set to select the PR1 output for this peripheral.

0

X2

System clock Control bit

Cleared to select the PR1 output for CPU and all the peripherals .

Set to bypass the PR1 prescaler and to enable the individual peripherals ‘X2’

bits.