Use of pll clock – Rainbow Electronics AT89C5122 User Manual

Page 47

47

AT8xC5122/23

4202E–SCR–06/06

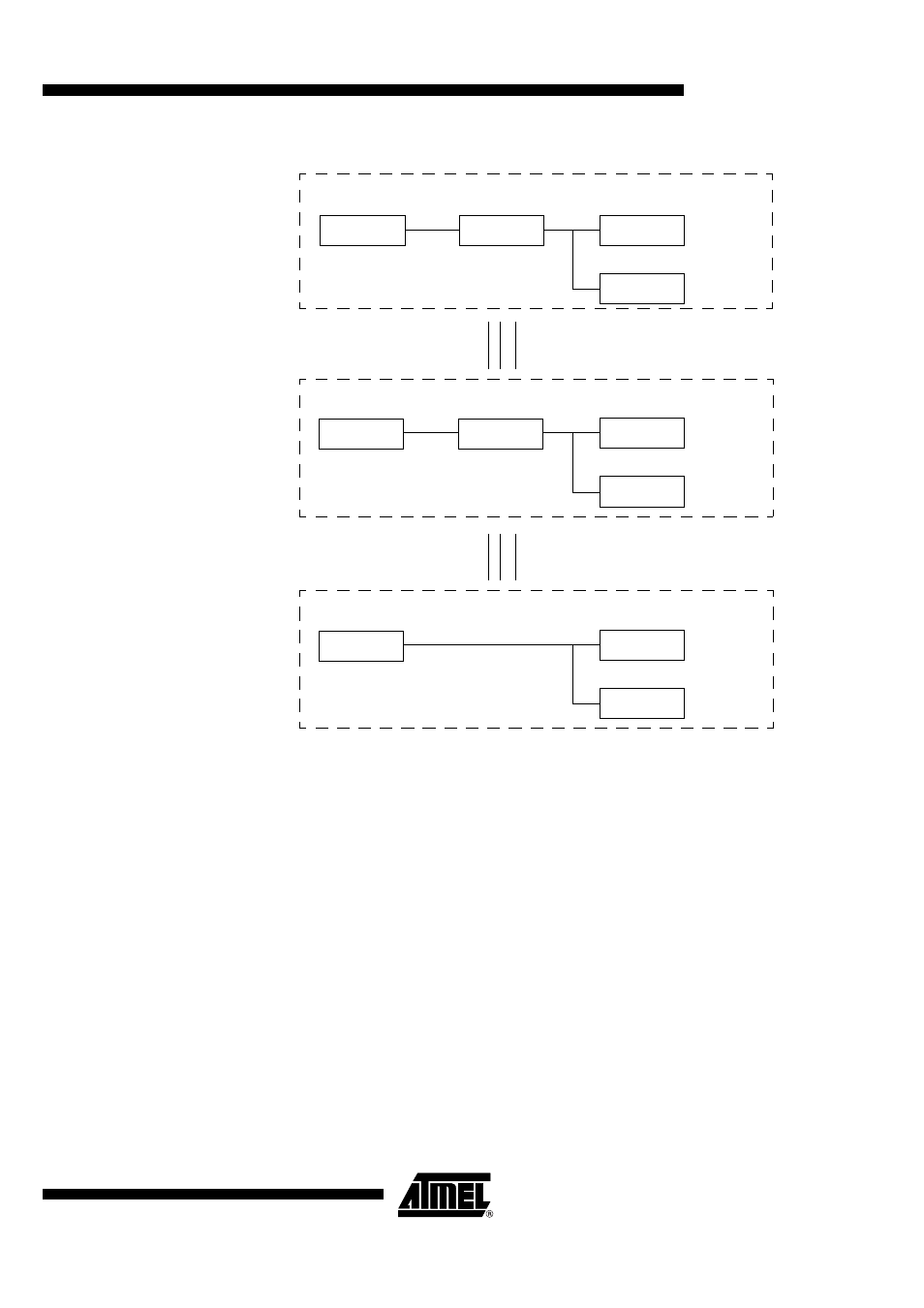

Use of PLL Clock

When the CPU clock is fed by the PLL, the X2 mode is forbidden. The bit X2 must

always remain cleared in CKCON0 register. As the PR1 prescaler is always different

from 1/2, the usual X1 mode can not be defined. So it is necessary to define an equiva-

lent X1 or X2 mode from equivalent clock circuits, as in previous section.

Example: PR1=1/4, PLL feeds the CPU. The CPU works in this case at 24 MHz. This

frequency could also be obtained by an equivalent clock circuit where the on-chip oscil-

lator would run at 48 MHz in X1 mode or at 24 Mhz in X2 mode. So we can say that in

this configuration, the CPU works at 48 MHz / X1 or 24 MHz / X2 (See figures below).

As the X2 bit is cleared in CKCON0 register, we have always F

CK_IDLE

= F

CK_PERIPH

.

8 MHz

CPU frequency

1 MHz

1/8

PR1 Prescaler

(Equivalent to)

2 MHz

1/2

External Clock

X1 mode selected

PERIPH frequency

1 MHz

CPU frequency

1 MHz

PERIPH frequency

1 MHz

(Equivalent to)

1 MHz

X2 mode selected

CPU frequency

1 MHz

PERIPH frequency

1 MHz

Crystal

External Clock