Clock tree architecture – Rainbow Electronics AT89C5122 User Manual

Page 43

43

AT8xC5122/23

4202E–SCR–06/06

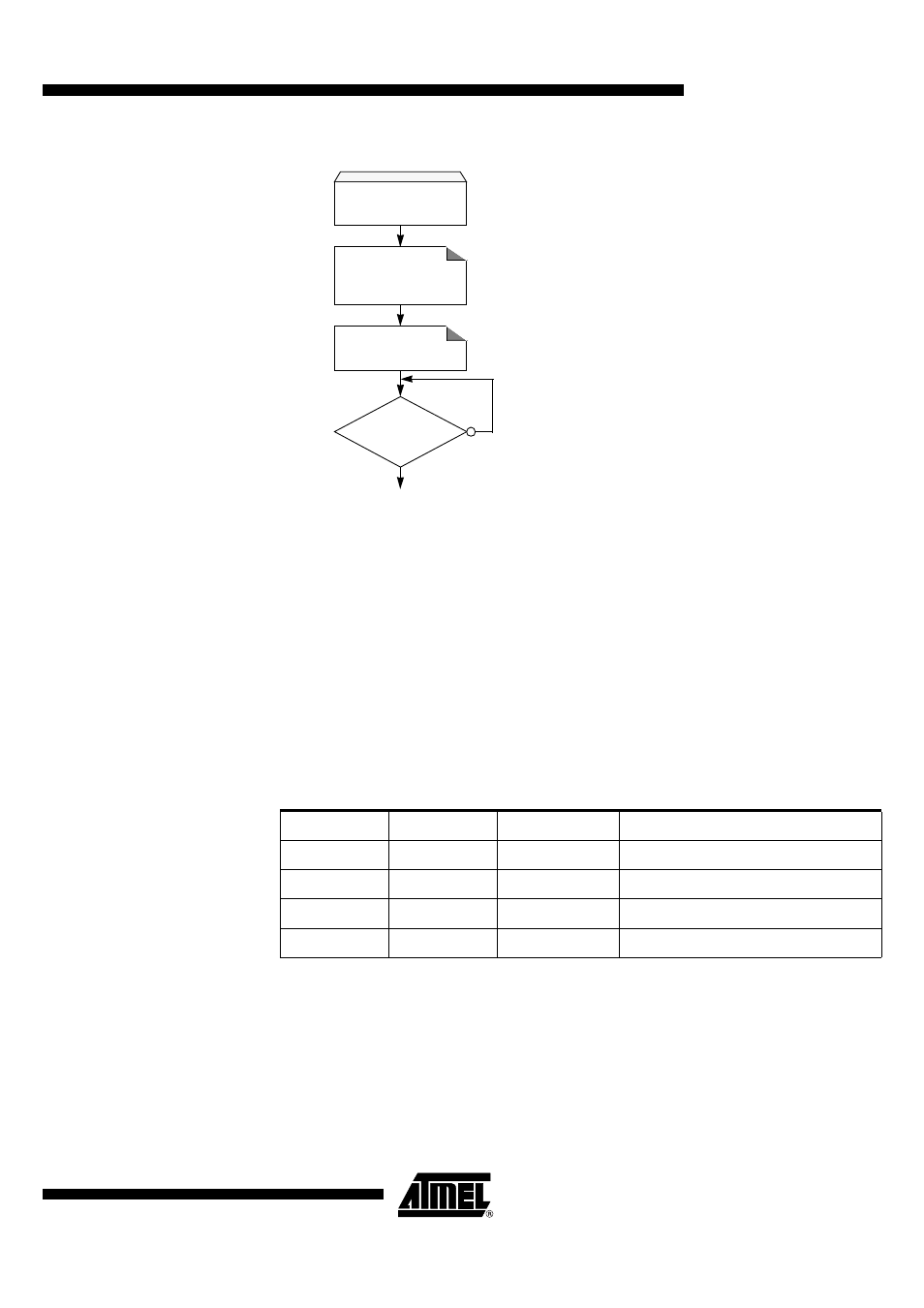

Figure 19. PLL Programming Flow

Clock Tree Architecture

The clock controller outputs several different clocks as shown in Figure 20:

•

a clock for the CPU core

•

a clock for the peripherals which is used to generate the timers, watchdog, SPI,

UART, and ports sampling clocks. This divided clock will be used to generate the

alternate card clock.

•

a clock for the USB

•

a clock for the SCIB controller

•

a clock for the DC/DC converter

These clocks are enabled or not depending on the power reduction mode as detailed in

Section “Power Management”, page 180.

These clocks are generated using four presacalers defined in the table below:

PLL

Programming

Configure Dividers

N3:0=

xxxxb

R3:0=

xxxxb

Enable PLL

PLLEN= 1

PLL Locked?

PLOCK= 1?

Prescaler

Register

Reload Factor

Function

PR1

CKRL

CKRL[0:3]

CPU & Peripheral clocks

PR2

SCICLK

SCICLK[0:5]

Smart card

PR3

SCSR

ALTKPS[0:1]

Alternate card

PR4

DCCKPS

DCCKPS[3:0]

DC/DC

- MAX14514 (14 pages)

- MAX16825 (15 pages)

- MAX16800 (9 pages)

- MAX6931 (14 pages)

- MAX6920 (10 pages)

- MAX6959 (19 pages)

- MAX15025 (16 pages)

- EVK2 (2 pages)

- MAX13256 (17 pages)

- MAX6964 (23 pages)

- MAX6948B (28 pages)

- MAX17117 (22 pages)

- MAX6934 (16 pages)

- MAX5048 (9 pages)

- MAX15054 (9 pages)

- AT6010LV (28 pages)

- AT83C24NDS (42 pages)

- AT83C21GC (6 pages)

- AT42QT1012 (6 pages)

- ATF16LV8C (11 pages)

- ATA6823 (28 pages)

- 71M6542G (165 pages)

- ATV2500BQL (21 pages)

- ATV750BL (19 pages)

- ATA6839 (17 pages)

- BA6229 (3 pages)

- ATF16V8C (18 pages)

- ATMOS™ 1M60 (26 pages)

- ATF1504ASVL (29 pages)

- BA6955N (9 pages)

- ATF1500ABV (15 pages)

- BA6219BFP-Y (7 pages)

- AT77C102B (19 pages)

- AT90SCR050 (4 pages)

- BA6208F (2 pages)

- ATA6625 (22 pages)

- ATA6664 (20 pages)

- ATF1516ASL (13 pages)

- ATF20V8BQL (18 pages)

- ATA6827 (15 pages)

- AT83C26 (77 pages)

- AT77C104B (36 pages)

- ATA6830 (23 pages)

- AT42QT1040 (18 pages)

- ATA6824 (22 pages)