Rainbow Electronics AT89C5131 User Manual

Page 144

144

AT89C5131

4136A–USB–03/03

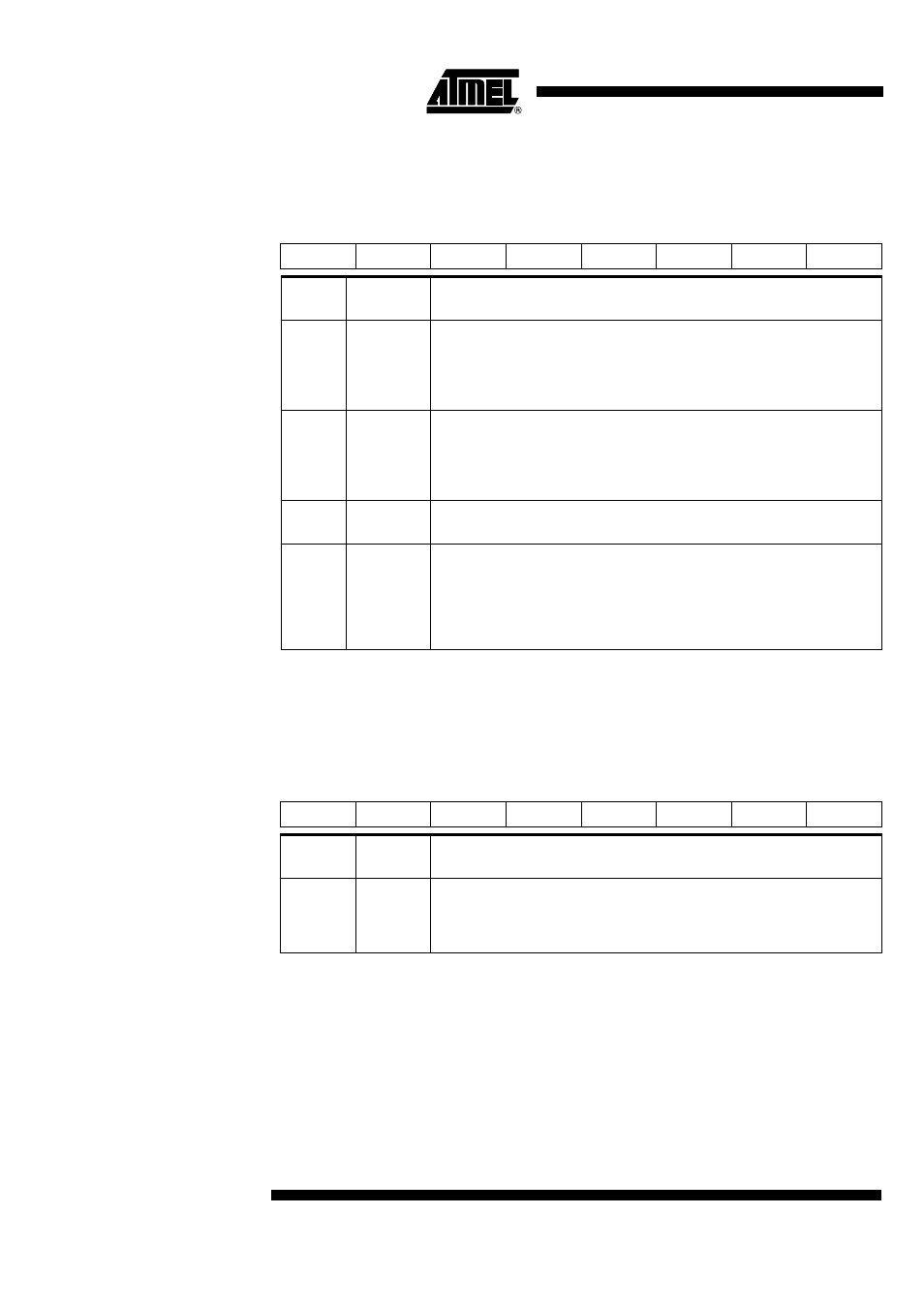

Table 96. UFNUMH Register

UFNUMH (S:BBh, read-only)

USB Frame Number High Register

Reset Value = 00h

Table 97. UFNUML Register

UFNUML (S:BAh, read-only)

USB Frame Number Low Register

Reset Value = 00h

7

6

5

4

3

2

1

0

-

-

CRCOK

CRCERR

-

FNUM10

FNUM9 FNUM8

Bit

Number

Bit

Mnemonic

Description

5

CRCOK

Frame Number CRC OK

This bit is set by hardware when a new Frame Number in Start of Frame Packet

is received without CRC error.

This bit is updated after every Start of Frame packet receipt.

Important note: the Start of Frame interrupt is generated just after the PID receipt.

4

CRCERR

Frame Number CRC Error

This bit is set by hardware when a corrupted Frame Number in Start of Frame

packet is received.

This bit is updated after every Start of Frame packet receipt.

Important note: the Start of Frame interrupt is generated just after the PID receipt.

3

-

Reserved

The value read from this bit is always 0. Do not set this bit.

2-0

FNUM[10:8]

Frame Number

FNUM[10:8] are the upper 3 bits of the 11-bit Frame Number (see the “UFNUML

Register UFNUML (S:BAh, read-only) USB Frame Number Low Register” on

page 144). It is provided in the last received SOF packet (see SOFINT in the

“USBIEN Register USBIEN (S:BEh) USB Global Interrupt Enable Register” on

page 135). FNUM is updated if a corrupted SOF is received.

7

6

5

4

3

2

1

0

FNUM7

FNUM6

FNUM5

FNUM4

FNUM3

FNUM2

FNUM1 FNUM0

Bit Number

Bit

Mnemonic Description

7 - 0

FNUM[7:0]

Frame Number

FNUM[7:0] are the lower 8 bits of the 11-bit Frame Number (See “UFNUMH

Register UFNUMH (S:BBh, read-only) USB Frame Number High Register” on

page 144).