Usb registers – Rainbow Electronics AT89C5131 User Manual

Page 133

133

AT89C5131

4136A–USB–03/03

USB Registers

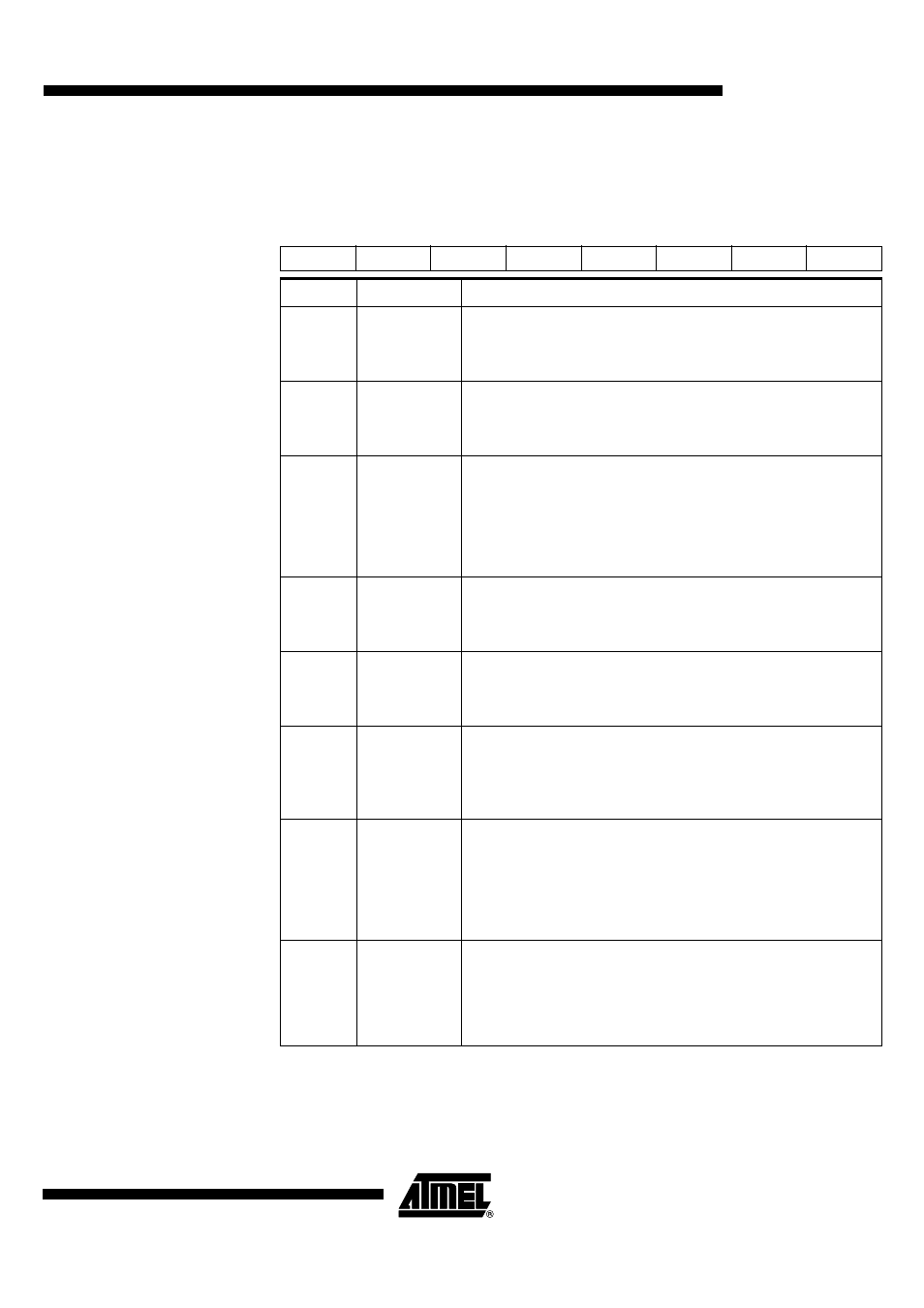

Table 83. USBCON Register

USBCON (S:BCh)

USB Global Control Register

Reset Value = 00h

7

6

5

4

3

2

1

0

USBE

SUSPCLK

SDRMWUP

DETACH

UPRSM

RMWUPE

CONFG FADDEN

Bit Number

Bit Mnemonic

Description

7

USBE

USB Enable

Set this bit to enable the USB controller.

Clear this bit to disable and reset the USB controller, to disable the USB

transceiver an to disable the USB controller clock inputs.

6

SUSPCLK

Suspend USB Clock

Set this bit to disable the 48 MHz clock input (Resume Detection is still

active).

Clear this bit to enable the 48 MHz clock input.

5

SDRMWUP

Send Remote Wake Up

Set this bit to force an external interrupt on the USB controller for Remote

Wake UP purpose.

An upstream resume is send only if the bit RMWUPE is set, all USB clocks

are enabled AND the USB bus was in SUSPEND state for at least 5 ms.

See UPRSM below.

This bit is cleared by software.

4

DETACH

Detach Command

Set this bit to simulate a Detach on the USB line. The V

REF

pin is then in a

floating state.

Clear this bit to maintain V

REF

at 3.3V.

3

UPRSM

Upstream Resume (read only)

This bit is set by hardware when SDRMWUP has been set and if RMWUPE

is enabled.

This bit is cleared by hardware after the upstream resume has been sent.

2

RMWUPE

Remote Wake-Up Enable

Set this bit to enabled request an upstream resume signaling to the host.

Clear this bit otherwise.

Note: Do not set this bit if the host has not set the

DEVICE_REMOTE_WAKEUP feature for the device.

1

CONFG

Configured

This bit will be set by the device firmware after a SET_CONFIGURATION

request with a non-zero value has been correctly processed.

It will be cleared by the device firmware when a SET_CONFIGURATION

request with a zero value is received. It is cleared by hardware on hardware

reset or when an USB reset is detected on the bus (SE0 state for at least 32

Full Speed bit times: typically 2.7

µ

s).

0

FADDEN

Function Address Enable

This bit will be set by the device firmware after a successful status phase of

a SET_ADDRESS transaction.

It will not be cleared afterwards by the device firmware. It is cleared by

hardware on hardware reset or when an USB reset is received (see above).

When this bit is cleared, the default function address is used (0).