Rainbow Electronics AT89C5131 User Manual

Page 141

141

AT89C5131

4136A–USB–03/03

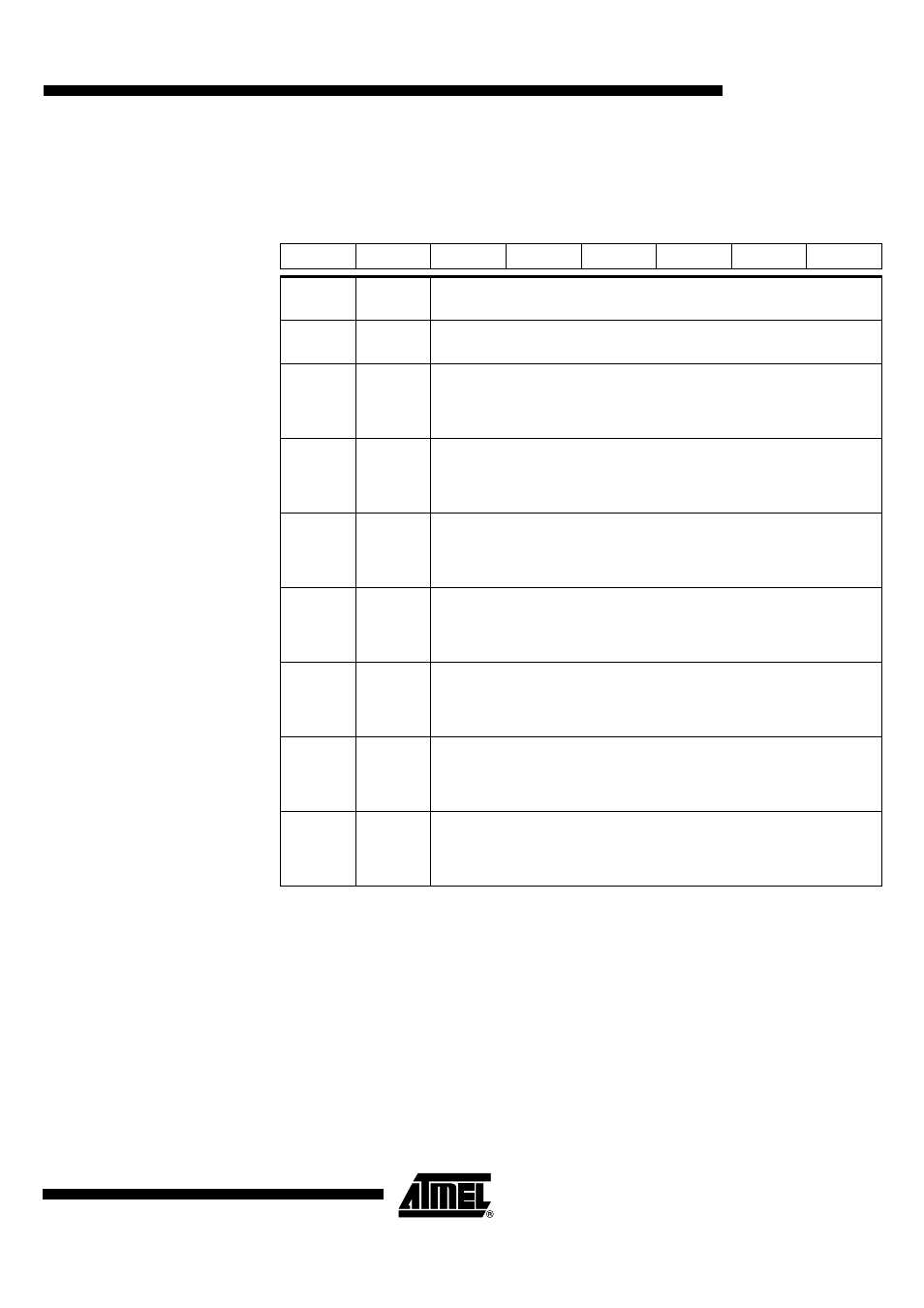

Table 93. UEPRST Register

UEPRST (S:D5h)

USB Endpoint FIFO Reset Register

Reset Value = 00h

7

6

5

4

3

2

1

0

-

EP6RST

EP5RST

EP4RST

EP3RST

EP2RST

EP1RST

EP0RST

Bit Number

Bit

Mnemonic Description

7

-

Reserved

The value read from this bit is always 0. Do not set this bit.

6

EP6RST

Endpoint 6 FIFO Reset

Set this bit and reset the endpoint FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

Then, clear this bit to complete the reset operation and start using the FIFO.

5

EP5RST

Endpoint 5 FIFO Reset

Set this bit and reset the endpoint FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

Then, clear this bit to complete the reset operation and start using the FIFO.

4

EP4RST

Endpoint 4 FIFO Reset

Set this bit and reset the endpoint FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

Then, clear this bit to complete the reset operation and start using the FIFO.

3

EP3RST

Endpoint 3 FIFO Reset

Set this bit and reset the endpoint FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

Then, clear this bit to complete the reset operation and start using the FIFO.

2

EP2RST

Endpoint 2 FIFO Reset

Set this bit and reset the endpoint FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

Then, clear this bit to complete the reset operation and start using the FIFO.

1

EP1RST

Endpoint 1 FIFO Reset

Set this bit and reset the endpoint FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

Then, clear this bit to complete the reset operation and start using the FIFO.

0

EP0RST

Endpoint 0 FIFO Reset

Set this bit and reset the endpoint FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

Then, clear this bit to complete the reset operation and start using the FIFO.