Serial peripheral interface (spi), Features, Signal description – Rainbow Electronics AT89C5131 User Manual

Page 104

104

AT89C5131

4136A–USB–03/03

Serial Peripheral

Interface (SPI)

The Serial Peripheral Interface module (SPI) allows full-duplex, synchronous, serial

communication between the MCU and peripheral devices, including other MCUs.

Features

Features of the SPI module include the following:

•

Full-duplex, three-wire synchronous transfers

•

Master or Slave operation

•

Eight programmable Master clock rates

•

Serial clock with programmable polarity and phase

•

Master mode fault error flag with MCU interrupt capability

•

Write collision flag protection

Signal Description

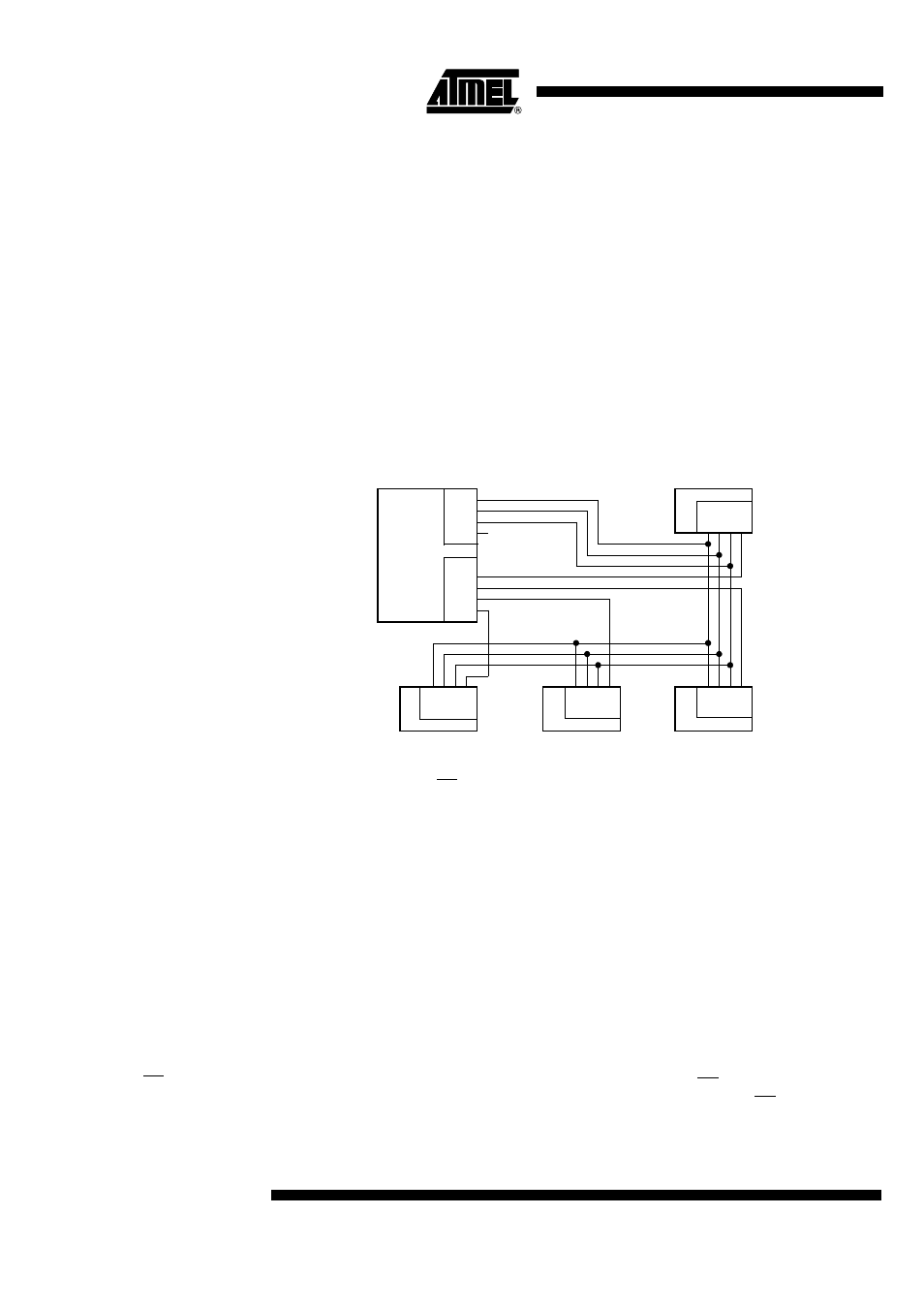

Figure 42 shows a typical SPI bus configuration using one Master controller and many

Slave peripherals. The bus is made of three wires connecting all the devices:

Figure 42. SPI Master/Slaves Interconnection

The Master device selects the individual Slave devices by using four pins of a parallel

port to control the four SS pins of the Slave devices.

Master Output Slave Input

(MOSI)

This 1-bit signal is directly connected between the Master Device and a Slave Device.

The MOSI line is used to transfer data in series from the Master to the Slave. Therefore,

it is an output signal from the Master, and an input signal to a Slave. A byte (8-bit word)

is transmitted most significant bit (MSB) first, least significant bit (LSB) last.

Master Input Slave Output

(MISO)

This 1-bit signal is directly connected between the Slave Device and a Master Device.

The MISO line is used to transfer data in series from the Slave to the Master. Therefore,

it is an output signal from the Slave, and an input signal to the Master. A byte (8-bit

word) is transmitted most significant bit (MSB) first, least significant bit (LSB) last.

SPI Serial Clock (SCK)

This signal is used to synchronize the data movement both in and out the devices

through their MOSI and MISO lines. It is driven by the Master for eight clock cycles

which allows to exchange one byte on the serial lines.

Slave Select (SS)

Each Slave peripheral is selected by one Slave Select pin (SS). This signal must stay

low for any message for a Slave. It is obvious that only one Master (SS high level) can

drive the network. The Master may select each Slave device by software through port

Slave 1

MI

S

O

MO

S

I

SCK

SS

MISO

MOSI

SCK

SS

PO

R

T

0

1

2

3

Slave 3

MIS

O

MOS

I

SC

K

SS

Slave 4

MI

S

O

MO

S

I

SCK

SS

Slave 2

MIS

O

MOS

I

SCK

SS

VDD

Master