Bulk/interrupt transactions – Rainbow Electronics AT89C5131 User Manual

Page 120

120

AT89C5131

4136A–USB–03/03

Bulk/Interrupt

Transactions

Bulk and Interrupt transactions are managed in the same way.

Bulk/Interrupt OUT

Transactions in Standard

Mode

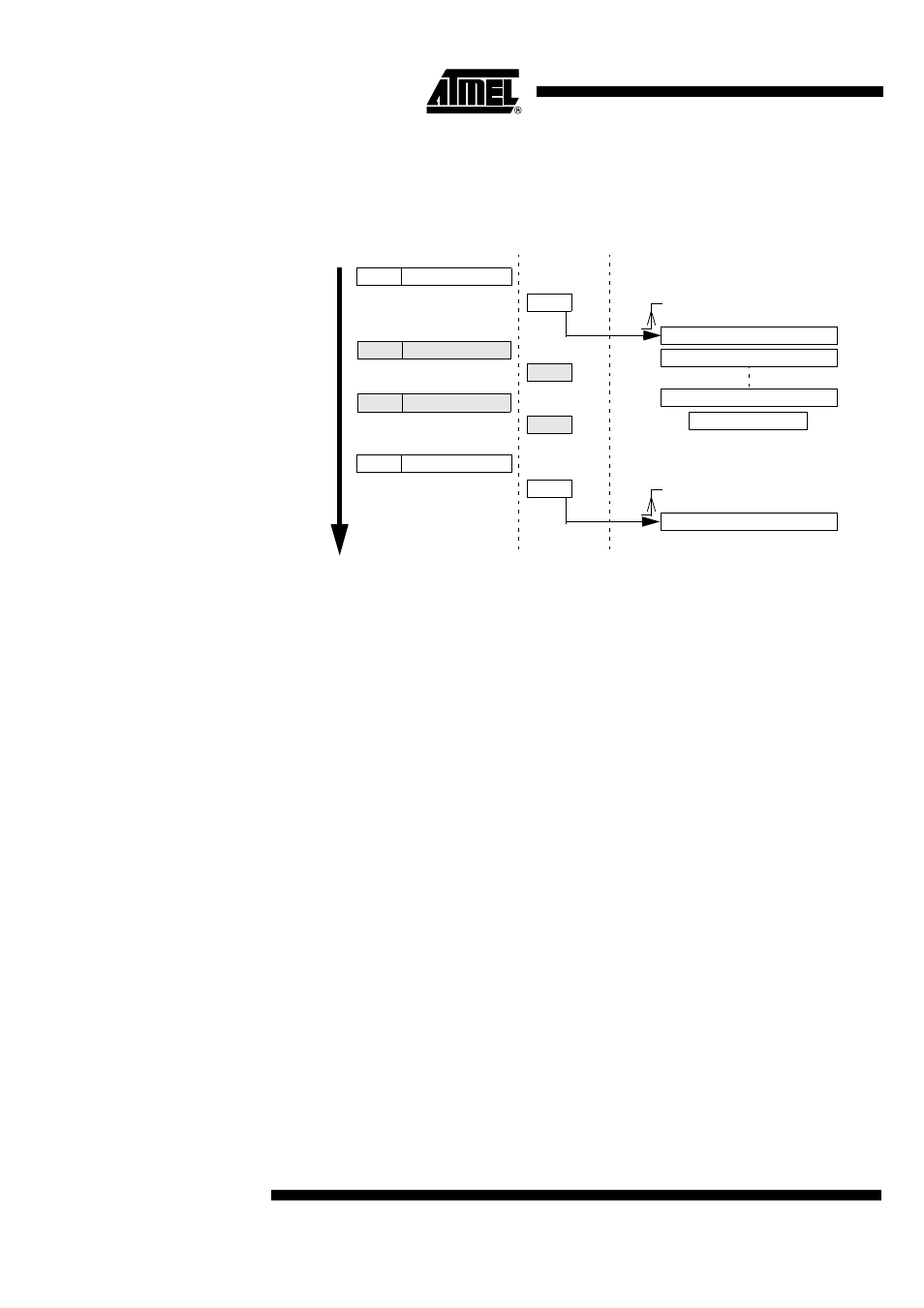

Figure 55. Bulk/Interrupt OUT transactions in Standard Mode

An endpoint will be first enabled and configured before being able to receive Bulk or

Interrupt packets.

When a valid OUT packet is received on an endpoint, the RXOUTB0 bit is set by the

USB controller. This triggers an interrupt if enabled. The firmware has to select the cor-

responding endpoint, store the number of data bytes by reading the UBYCTLX and

UBYCTHX registers. If the received packet is a ZLP (Zero Length Packet), the

UBYCTLX and UBYCTHX register values are equal to 0 and no data has to be read.

When all the endpoint FIFO bytes have been read, the firmware will clear the RXOUTB0

bit to allow the USB controller to accept the next OUT packet on this endpoint. Until the

RXOUTB0 bit has been cleared by the firmware, the USB controller will answer a NAK

handshake for each OUT requests.

If the Host sends more bytes than supported by the endpoint FIFO, the overflow data

won’t be stored, but the USB controller will consider that the packet is valid if the CRC is

correct and the endpoint byte counter contains the number of bytes sent by the Host.

OUT

DATA0 (n bytes)

ACK

HOST

UFI

C51

Endpoint FIFO read byte 1

OUT

DATA1

NAK

RXOUTB0

Endpoint FIFO read byte 2

Endpoint FIFO read byte n

Clear RXOUTB0

OUT

DATA1

NAK

OUT

DATA1

ACK

RXOUTB0

Endpoint FIFO read byte 1