Rainbow Electronics AT89C5131 User Manual

Page 134

134

AT89C5131

4136A–USB–03/03

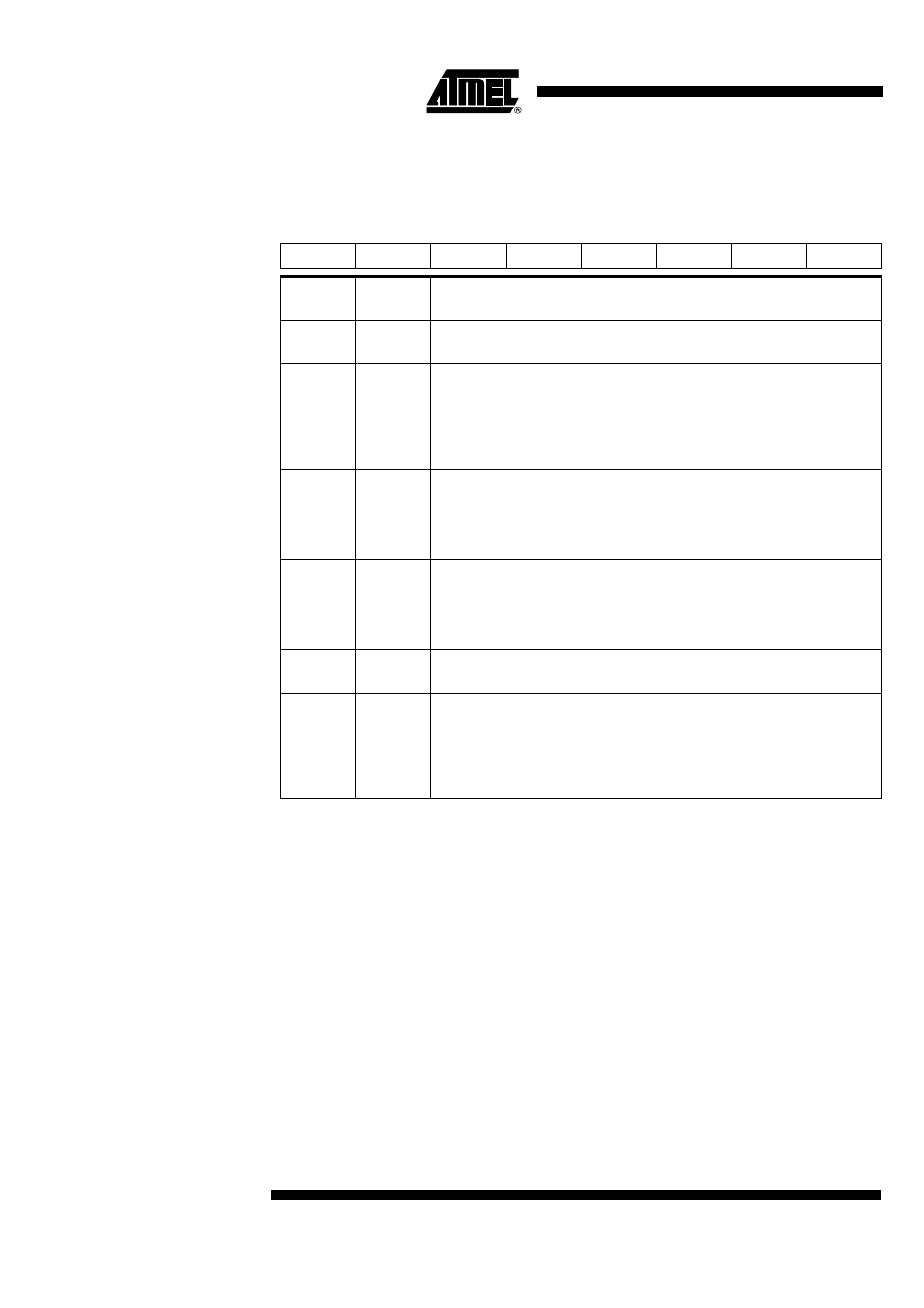

Table 84. USBINT Register

USBINT (S:BDh)

USB Global Interrupt Register

Reset Value = 00h

7

6

5

4

3

2

1

0

-

-

WUPCPU

EORINT

SOFINT

-

- SPINT

Bit Number

Bit

Mnemonic Description

7-6

-

Reserved

The value read from these bits is always 0. Do not set these bits.

5

WUPCPU

Wake Up CPU Interrupt

This bit is set by hardware when the USB controller is in SUSPEND state and is

re-activated by a non-idle signal FROM USB line (not by an upstream resume).

This triggers a USB interrupt when EWUPCPU is set in Figure 85 on page 135.

When receiving this interrupt, user has to enable all USB clock inputs.

This bit will be cleared by software (USB clocks must be enabled before).

4

EORINT

End Of Reset Interrupt

This bit is set by hardware when a End Of Reset has been detected by the USB

controller. This triggers a USB interrupt when EEORINT is set in the Figure 85

(see Figure 85 on page 135).

This bit will be cleared by software.

3

SOFINT

Start of Frame Interrupt

This bit is set by hardware when an USB Start of Frame PID (SOF) has been

detected. This triggers a USB interrupt when ESOFINT is set in the Figure 85

(see Figure 85 on page 135).

This bit will be cleared by software.

2-1

-

Reserved

The value read from these bits is always 0. Do not set these bits.

0

SPINT

Suspend Interrupt

This bit is set by hardware when a USB Suspend (Idle bus for three frame

periods: a J state for 3 ms) is detected. This triggers a USB interrupt when

ESPINT is set in see Figure 85 on page 135.

This bit will be cleared by software BEFORE any other USB operation to re-

activate the macro.