Rainbow Electronics AT89C5131 User Manual

Page 131

131

AT89C5131

4136A–USB–03/03

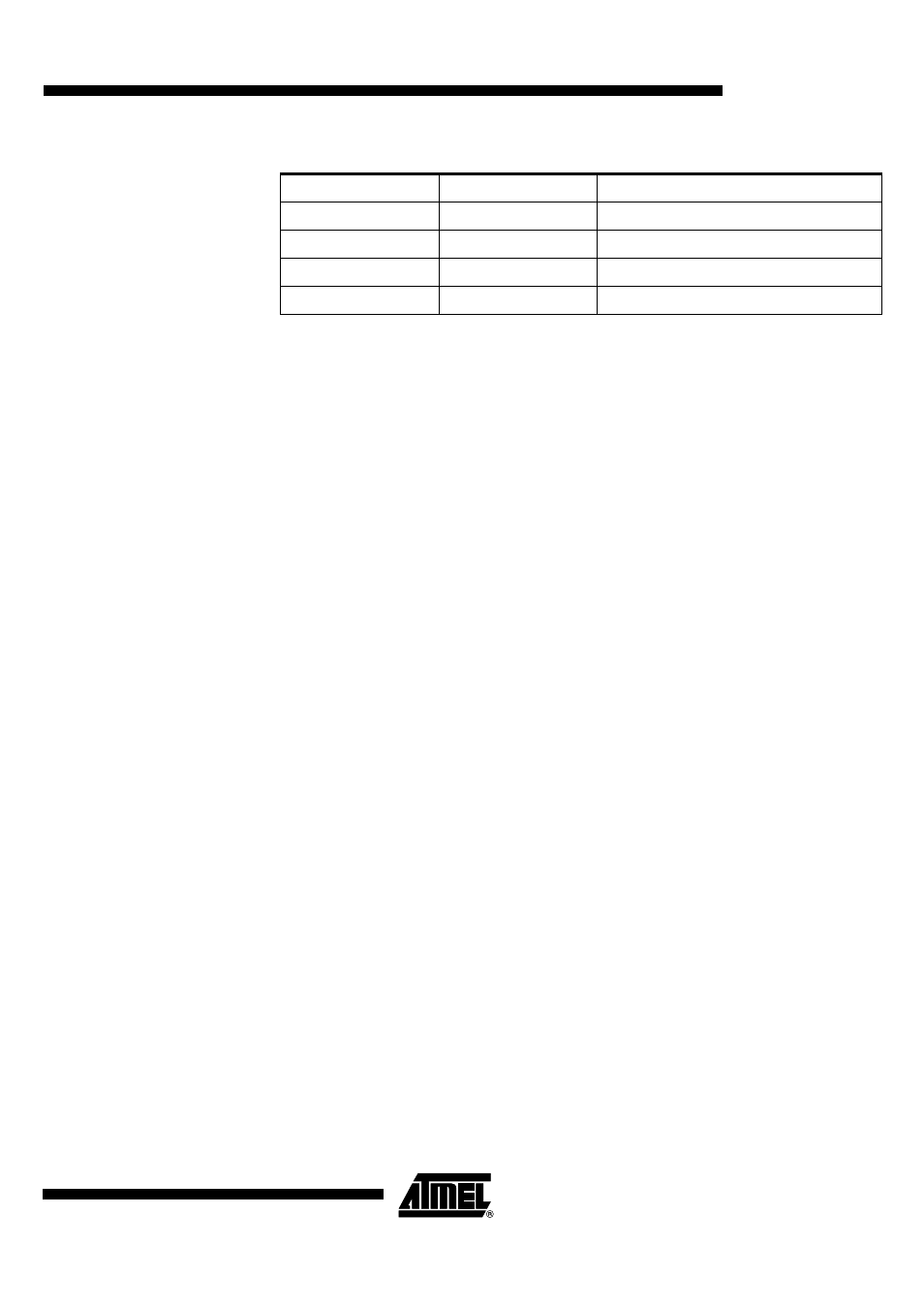

Table 82. Priority Levels

USB Interrupt Control System

As shown in Figure 64, many events can produce a USB interrupt:

•

TXCMPL: Transmitted In Data (see Table 89 on page 138). This bit is set by

hardware when the Host accept a In packet.

•

RXOUTB0: Received Out Data Bank 0 (see Table 89 on page 138). This bit is set

by hardware when an Out packet is accepted by the endpoint and stored in bank 0.

•

RXOUTB1: Received Out Data Bank 1 (only for Ping-pong endpoints) (see Table 89

on page 138). This bit is set by hardware when an Out packet is accepted by the

endpoint and stored in bank 1.

•

RXSETUP: Received Setup (see Table 89 on page 138). This bit is set by hardware

when an SETUP packet is accepted by the endpoint.

•

STLCRC: STALLED (only for Control, Bulk and Interrupt endpoints) (see Table 89

on page 138). This bit is set by hardware when a STALL handshake has been sent

as requested by STALLRQ, and is reset by hardware when a SETUP packet is

received.

•

SOFINT: Start of Frame Interrupt (See “USBIEN Register USBIEN (S:BEh) USB

Global Interrupt Enable Register” on page 135). This bit is set by hardware when a

USB Start of Frame packet has been received.

•

WUPCPU: Wake-Up CPU Interrupt (See “USBIEN Register USBIEN (S:BEh) USB

Global Interrupt Enable Register” on page 135). This bit is set by hardware when a

USB resume is detected on the USB bus, after a SUSPEND state.

•

SPINT: Suspend Interrupt (See “USBIEN Register USBIEN (S:BEh) USB Global

Interrupt Enable Register” on page 135). This bit is set by hardware when a USB

suspend is detected on the USB bus.

IPHUSB

IPLUSB

USB Priority Level

0

0

0 Lowest

0

1

1

1

0

2

1

1

3

Highest