Texas Instruments TMS380C26 User Manual

Page 81

TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL 1992–REVISED MARCH 1993

POST OFFICE BOX 1443

•

HOUSTON, TEXAS

77251–1443

81

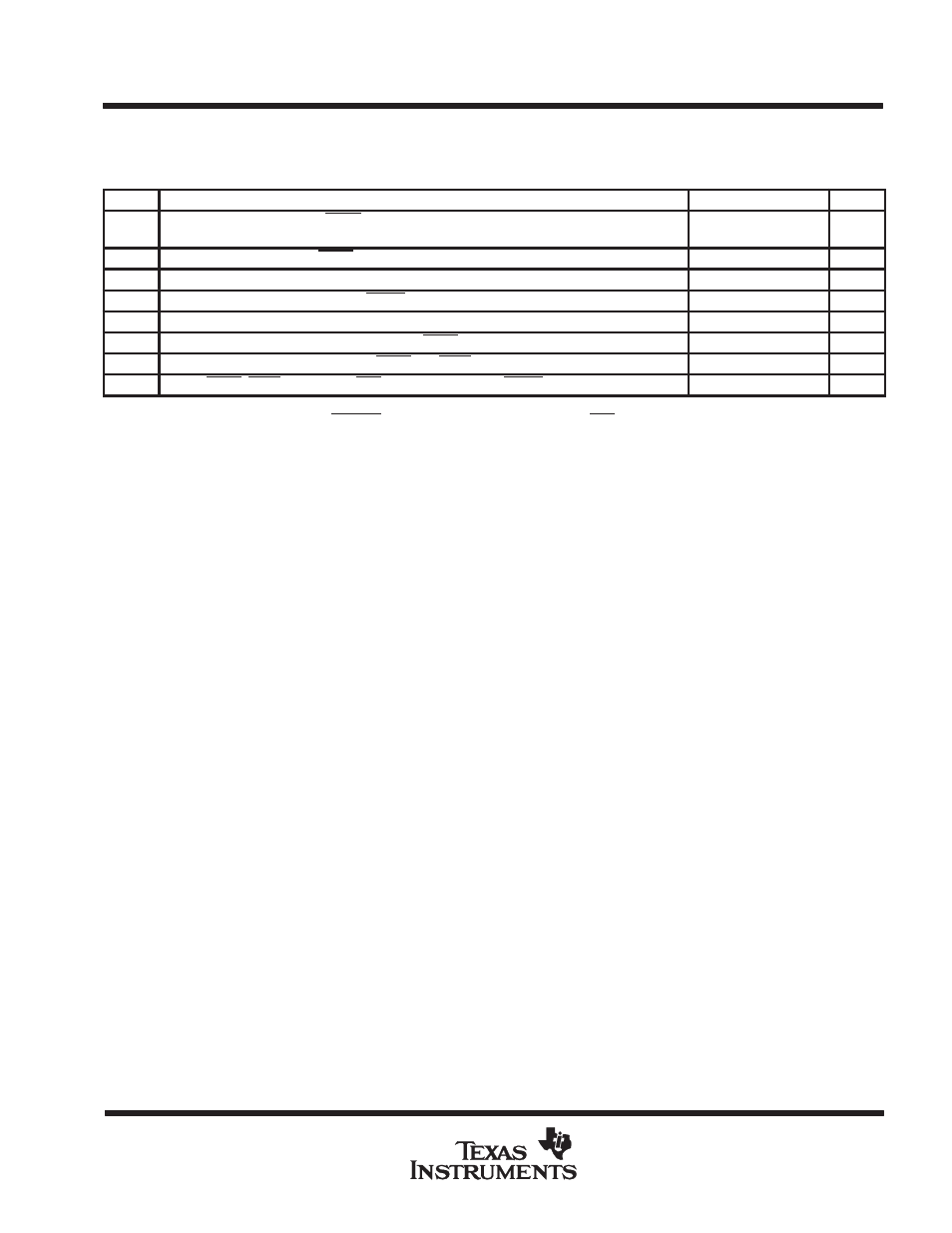

PARAMETER MEASUREMENT INFORMATION

68xxx mode bus arbitration timing, SIF takes control

NO.

PARAMETER

MIN

MAX

UNIT

208a

Setup of asynchronous input SBGR before SBCLK no longer high to guarantee recognition on

this cycle

15

ns

208b

Hold of asynchronous input SBGR after SBCLK low to guarantee recognition on this cycle

15

ns

212

Delay from SBCLK low to address valid

25

ns

224a

Delay from SBCLK low in cycle I2 to SOWN low (see Note 24)

25

ns

224c

Delay from SBCLK low in cycle I2 to SDDIR low in DMA read

30

ns

230

Delay from SBCLK high to either SHRQ low or SBRQ high

25

ns

241

Delay from SBCLK high in TX cycle to SUDS and SLDS high

25

ns

241a†

Hold of SUDS, SLDS, SRNW, and SAS high-impedance after SOWN low, bus acquisition

tc(SCK) – 15

ns

† This specification has been characterized to meet stated value.

NOTE 24: Motorola-style bus slaves hold SDTACK active until the bus master deasserts SAS.