Sif adapter control register (sifacl) – Texas Instruments TMS380C26 User Manual

Page 26

TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL 1992–REVISED MARCH 1993

POST OFFICE BOX 1443

•

HOUSTON, TEXAS

77251–1443

26

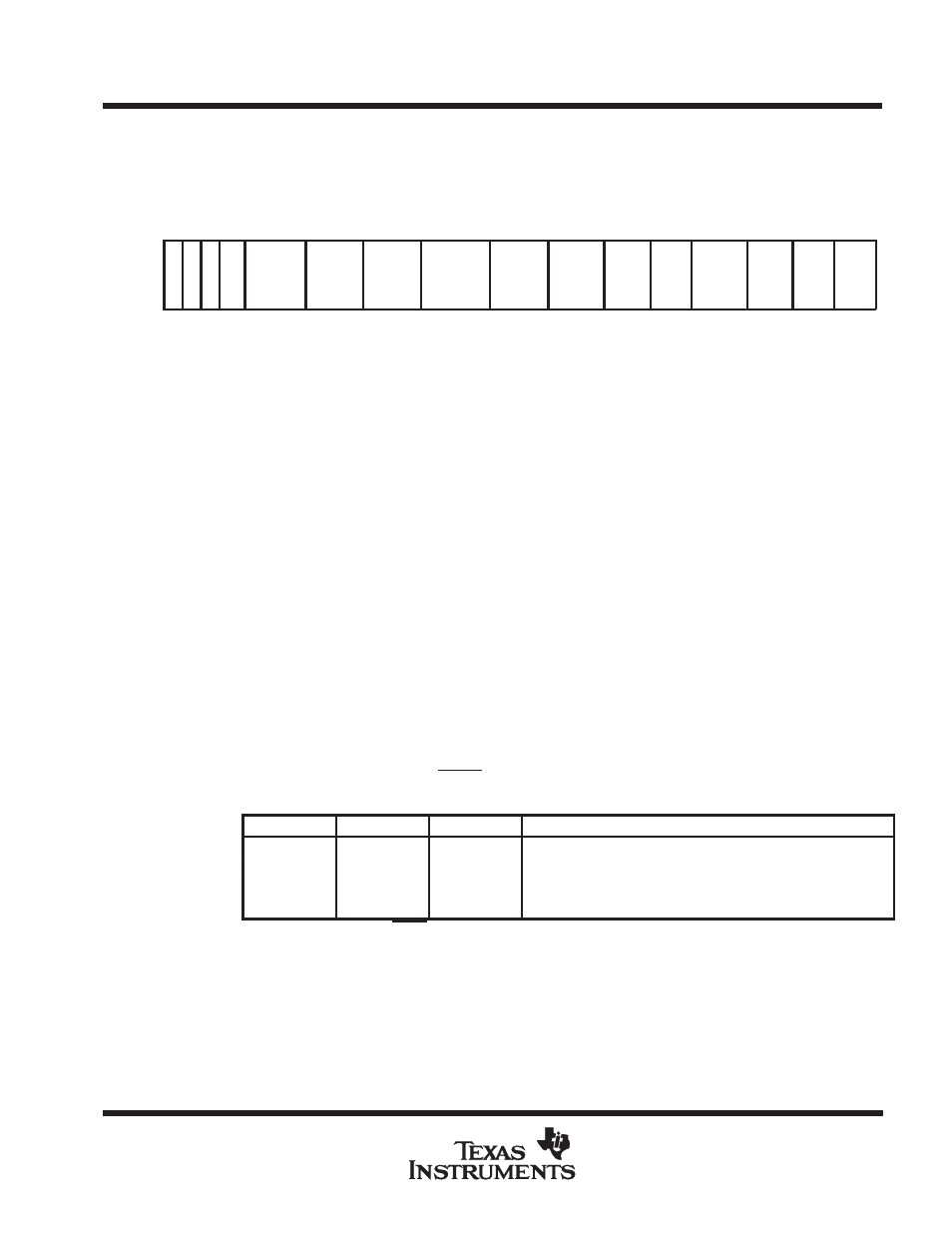

SIF Adapter Control Register (SIFACL)

The SIFACL register allows the host processor to control and to some extent reconfigure the

TMS380C26 under software control.

SIFACL Register

Bit #

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

T

E

S

T

0

T

E

S

T

1

T

E

S

T

2

—

SWHLDA

SWDDIR

SWHRQ

PSDMAEN

ARESET

CPHALT

BOOT

RES0

SINTEN

PEN

NSEL

OUT0

NSEL

OUT1

R

R

R

RP – 0

R – u

R – 0

RS – 0

RW – 0

RP – b

RP – b

R

RW – 1

RP – p

RP-0

RP–1

R = Read, W = Write, P = Write during ARESET = 1 only, S = Set Only,

– n = Value after reset

(b = Value on BTSTRP pin, p = Value on PRTYEN pin, u = Indeterminate)

Bits 0-2:

TEST (0 – 2). Value on TEST (0 – 2) pins.

These bits are read only and always reflect the value on the corresponding device pins. This

allows the host S/W to determine the network type and speed configuration. If the network speed

and type are software configurable, these bits can be used to determine which configurations

are supported by the network hardware.

TEST0

TEST1

TEST2

Description

L

L

H

Reserved

L

H

H

16 Mbps token ring

H

L

H

Ethernet (802.3/Blue Book)

H

H

H

4 Mbps token ring

X

X

0

Reserved

Bit 3:

Reserved. Read data is indeterminate.

Bit 4:

SWHLDA — Software Hold Acknowledge

This bit allows the SHLDA/SBGR pin’s function to be emulated from software control for

pseudo-DMA.

PSDMAEN

SWHLDA

SWHRQ

RESULT

0

†

X

X

SWHLDA value in the SIFACL register cannot be set to a one.

1

†

0

0

No pseudo-DMA request pending.

1

†

0

1

Indicates a pseudo-DMA request interrupt.

1

†

1

X

Pseudo-DMA process in progress.

† The value on the SHLDA/SBGR pin is ignored.

Bit 5:

SWDDIR — Current SDDIR Signal Value

This bit contains the current value of the pseudo-DMA direction. This enables the host to easily

determine the direction of DMA transfers, which allows system DMA to be controlled by system

software.

0

=

Pseudo-DMA from host system to TMS380C26.

1

=

Pseudo-DMA from TMS380C26 to host system.