Parameter measurement information – Texas Instruments TMS380C26 User Manual

Page 70

TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL

1992–REVISED MARCH 1993

70

POST

OFFICE BOX 1443 HOUST

ON,

TEXAS

77001

•

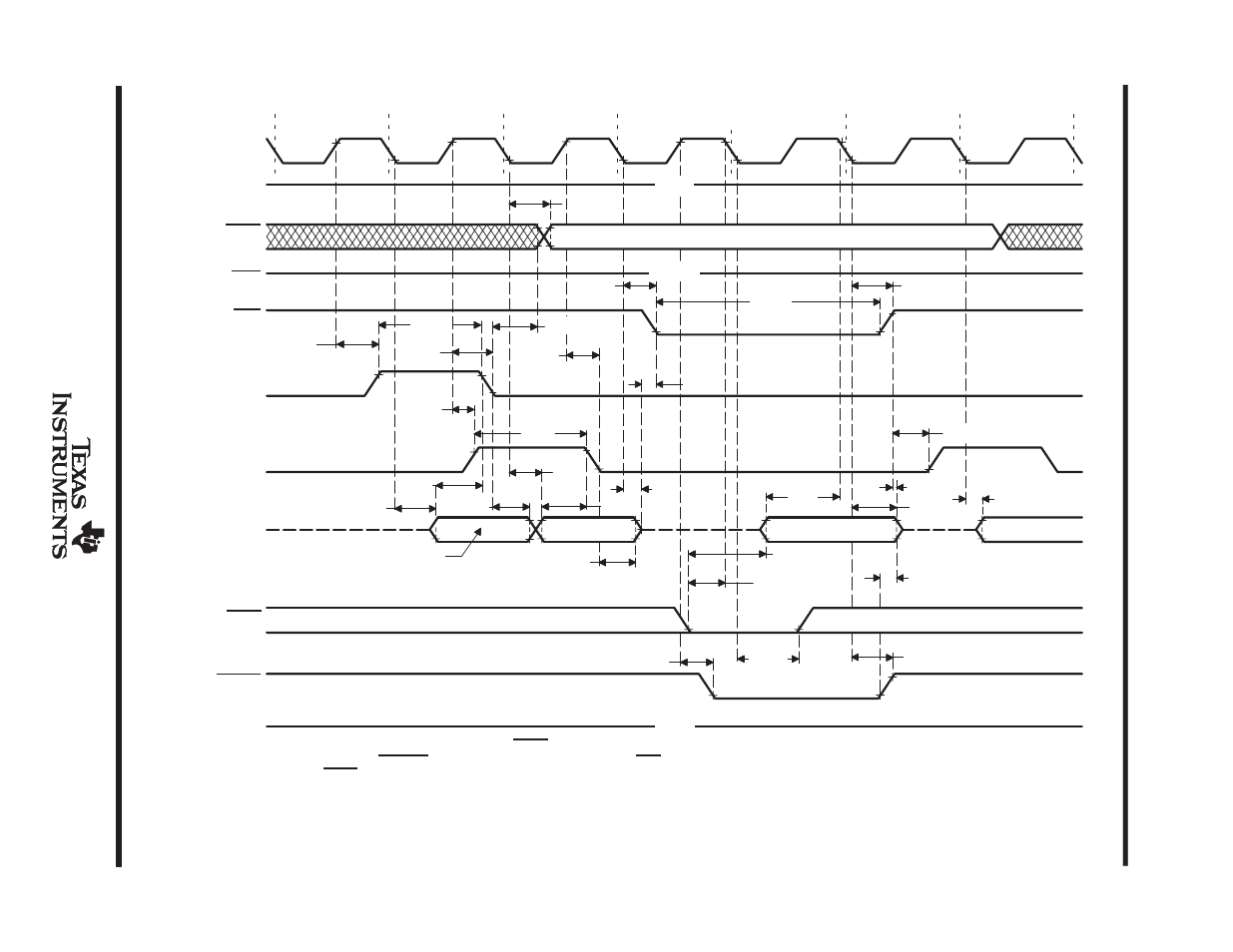

PARAMETER MEASUREMENT INFORMATION

214

Address

Data

Address

Extended

Address

Valid

Low

(High)

SDDIR

SDBEN

(see Note A)

SRDY

SADH0–SADH7,

SADL0–SADL7,

SPH, SPL

(see Note C)

SALE

SXAL

SRD

(see Note A)

SWR

SBHE

(see Note B)

SRAS

SBCLK

212

233

212

212

218

217

218

226

227R

223R

231

207a

205

247†

208a

208b

225R

229

237R

215

216

217

216

V

TWAIT

T1

T4

T3

T1

TX

T4

HI-Z

215

207b

216a

233

218

206

T2

† If parameter 208A is not met then valid data must be present before SRDY goes low.

NOTES: A. Motorola-style bus slaves hold SDTACK active until the bus master deasserts SAS.

B. In 8-bit 80x8x mode, SBHE/SRNW is a don’t care input during DIO and an inactive (high) output during DMA.

C. In 8-bit 80x8x mode, the most significant byte of the address is maintained on SADH for T2, T3, and T4. The address is maintained according to parameter 21; i.e., held

after T4 high.

Figure 33. 80x8x Mode DMA Read Timing