Texas Instruments TMS380C26 User Manual

Page 34

TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL 1992–REVISED MARCH 1993

POST OFFICE BOX 1443

•

HOUSTON, TEXAS

77251–1443

34

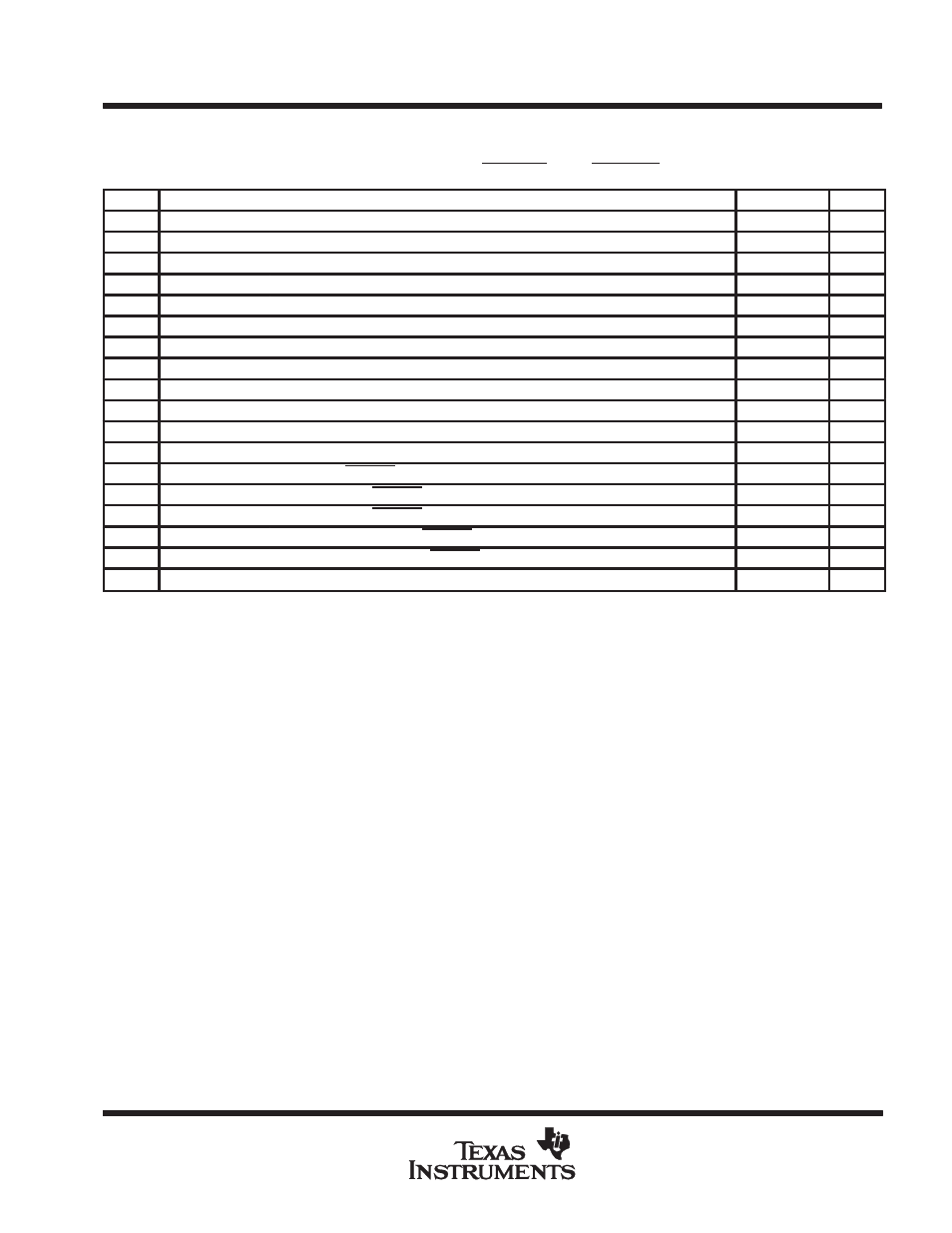

PARAMETER MEASUREMENT INFORMATION

power up, SBCLK, OSCIN, MBCLK1, MBCLK2, SYNCIN, and SRESET timing

NO.

PARAMETER

MIN

MAX

UNIT

100†

tr(VDD)

Rise time from 1.2 V to VDD minimum high level

1

ms

101†‡

td(VDDH-SCKV)

Delay time from minimum VDD high level to first valid SBCLK no longer high

1

ms

102†‡

td(VDDH-OSCV)

Delay time from minimum VDD high level to first valid OSCIN high

1

ms

103

tc(SCK)

Cycle time of SBCLK

62.5

ns

104

tw(SCKH)

Pulse duration of SBCLK high

26

ns

105

tw(SCKL)

Pulse duration of SBCLK low

26

ns

106†

tt(SCK)

Transition time of SBCLK

5

ns

107

tc(OSC)

Cycle time of OSCIN (see Note 12)

15.6

500

ns

108

tw(OSCH)

Pulse duration of OSCIN high

5.5

ns

109

tw(OSCL)

Pulse duration of OSCIN low

5.5

ns

110†

tt(OSC)

Transition time of OSCIN

3

ns

111†

td(OSCV-CKV)

Delay time from OSCIN valid to MBCLK1 and MBCLK2 valid

1

ms

117†

th(VDDH-RSL)

Hold time of SRESET low after VDD reaches minimum high level

5

ms

118†

tw(RSH)

Pulse duration of SRESET high

14

µ

s

119†

tw(RSL)

Pulse duration of SRESET low

14

µ

s

288†

tsu(RST)

Setup time of DMA size to SRESET high (Intel mode only)

15

ns

289†

th(RST)

Hold time of DMA size from SRESET high (Intel mode only)

15

ns

tM

One-eighth of an local memory cycle

2tc(OSC)

† This specification is provided as an aid to board design.

‡ If parameter 101 or 102 cannot be met, parameter 117 must be extended by the larger difference: real value of parameter 101 or 102 minus the

max value listed.

NOTE 12: If OSCIN is used to generate PXTALIN, the specification for the tolerance of OSCIN is equal to

±

0.01%.