Texas Instruments TMS380C26 User Manual

Page 73

TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL 1992–REVISED MARCH 1993

POST OFFICE BOX 1443

•

HOUSTON, TEXAS

77251–1443

73

PARAMETER MEASUREMENT INFORMATION

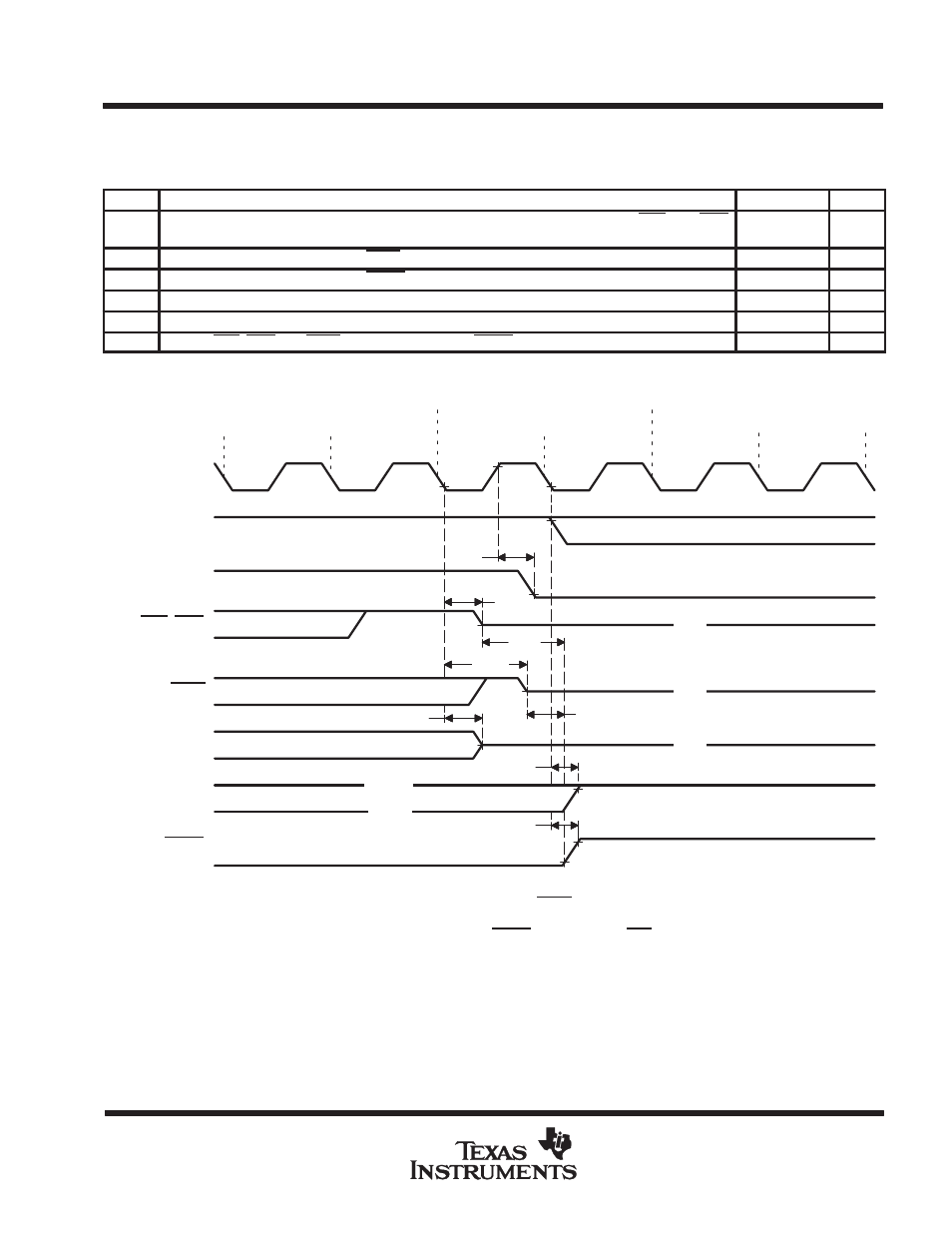

80x8x mode bus arbitration timing, SIF returns control

NO.

PARAMETER

MIN

MAX

UNIT

220†

Delay from SBCLK low in I1 cycle to SADH0–SADH7, SADL0–SADL7, SPL, SPH, SRD, and SWR

high-impedance

35

ns

223b†

Delay from SBCLK low in I1 cycle to SBHE high-impedance

45

ns

224b

Delay from SBCLK low in cycle I2 to SOWN high

25

ns

224d

Delay from SBCLK low in cycle I2 to SDDIR high

30

ns

230

Delay from SBCLK high in cycle I1 to SHRQ low

25

ns

240†

Setup of SRD, SWR, and SBHE high-impedance before SOWN no longer low

0

ns

† This specification has been characterized to meet stated value.

READ

WRITE

SIF

SIF

SOWN

(see Note B)

SDDIR

SADH0–SADH7,

SADL0–SADL7,

SPH, SPL

SBHE

SRD, SWR

SHRQ

(see Note A)

SIF Outputs:

SHLDA

SBCLK

User Master

Bus Exchange

SIF Master

(T2)

(T1)

I2

I1

T4

T3

224d

220

240

223b

240

220

HI-Z

HI-Z

HI-Z

224b

230

NOTES: A. In 80x8x mode, the system interface deasserts SHRQ on the rising edge of SBCLK following the T4 state of the last system bus

transfer it controls. In 68xxx mode, the system interface deasserts SBRQ on the rising edge of SBCLK in state T2 of the first system

bus transfer it controls.

B. While the system interface DMA controls are active (i.e., SOWN is asserted), the SCS input is disabled.

Figure 35. 80x8x Mode Bus Arbitration Timing, SIF Returns Control