Terminal functions (continued) – Texas Instruments TMS380C26 User Manual

Page 10

TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL 1992–REVISED MARCH 1993

POST OFFICE BOX 1443

•

HOUSTON, TEXAS

77251–1443

10

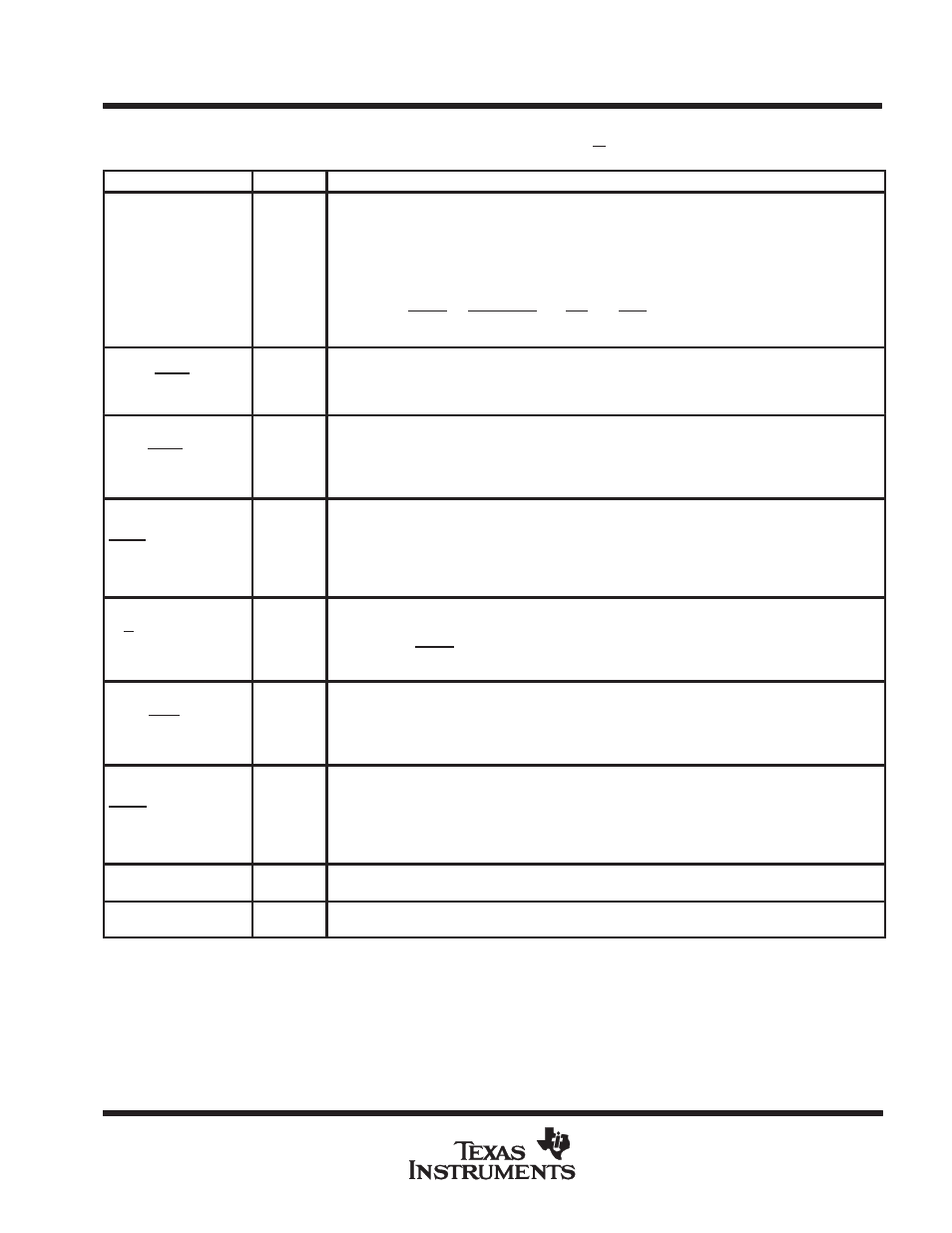

Terminal Functions (continued)

System Interface – Intel Mode (SI/M = H)

PIN NAME

NO.

I/O

DESCRIPTION

SDDIR

38

OUT

System Data Direction. This output provides to the external data buffers a signal indicating the direction

in which the data is moving. During DIO writes and DMA reads, SDDIR is low (data direction input to

the TMS380C26). During DIO reads and DMA writes, SDDIR is high (data direction output from the

TMS380C26). When the system interface is

NOT involved in a DIO or DMA operation, then SDDIR is

high by default.

DATA

SDDIR

DIRECTION

DIO

DMA

H

output

read

write

L

input

write

read

SHLDA/SBGR

37

IN

System Hold Acknowledge. This pin indicates that the system DMA hold request has been

acknowledged. It is internally synchronized to SBCLK (see Note 1).

H = Hold request acknowledged.

L

= Hold request not acknowledged.

SHRQ/SBRQ

56

OUT

System Hold Request. This pin is used to request control of the system bus in preparation for a DMA

transfer. This pin is internally synchronized to SBCLK.

H = System bus requested.

L

= System bus not requested.

SIACK

24

IN

System Interrupt Acknowledge. This signal is from the host processor to acknowledge the interrupt

request from the TMS380C26.

H = System interrupt not acknowledged (see Note 1).

L

= System interrupt acknowledged: the TMS380C26 places its interrupt vector onto the system

bus.

SI/M

35

IN

System Intel/Motorola Mode Select. The value on this pin specifies the system interface mode.

H = Intel-compatible interface mode selected. Intel interface can be 8-bit or 16-bit mode

(see S8/SHALT pin description and Note 1.)

L

= Motorola-compatible interface mode selected.

SINTR/SIRQ

36

OUT

System Interrupt Request. TMS380C26 activates this output to signal an interrupt request to the host

processor.

H = Interrupt request by TMS380C26.

L

= No interrupt request.

SOWN

59

OUT

System Bus Owned. This signal indicates to external devices that TMS380C26 has control of the

system bus. This signal drives the enable signal of the bus transceiver chips, which drive the address

and bus control signals.

H = TMS380C26 does not have control of the system bus.

L

= TMS380C26 has control of the system bus.

SPH

62

I/O

System Parity High. The optional odd-parity bit for each address or data byte transmitted over

SADH0-SADH7 (see Note 1).

SPL

55

I/O

System Parity Low. The optional odd-parity bit for each address or data byte transmitted over

SADL0-SADL7 (see Note 1).

NOTE 1: Pin has an internal pullup device to maintain a high voltage level when left unconnected (no etch or loads).