Texas Instruments TMS380C26 User Manual

Page 57

TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL 1992–REVISED MARCH 1993

POST OFFICE BOX 1443

•

HOUSTON, TEXAS

77251–1443

57

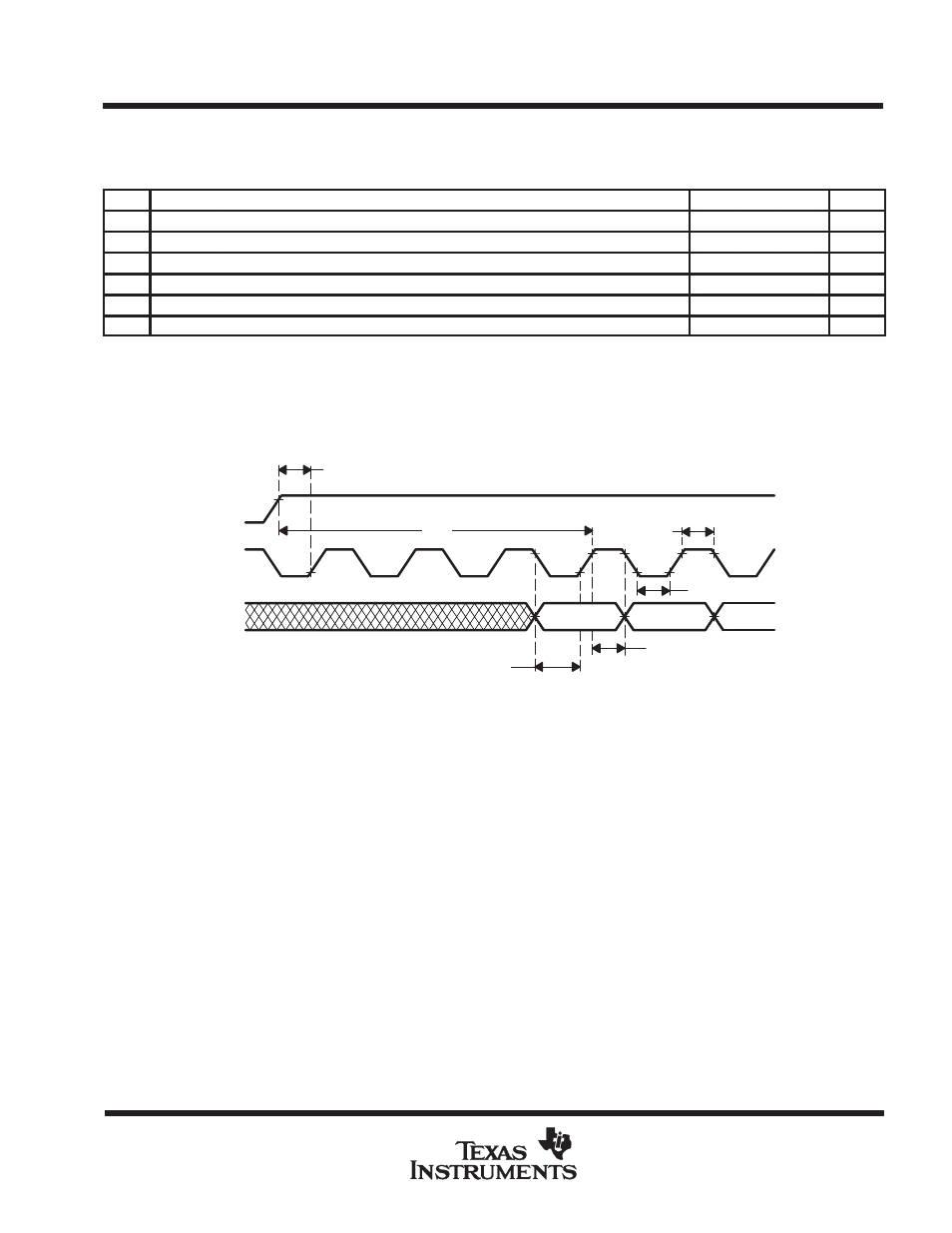

PARAMETER MEASUREMENT INFORMATION

ethernet timing of RCV signals — start of frame

NO.

PARAMETER

MIN

TYP

MAX

UNIT

310

RXDSET

Setup of RXD before RXC no longer low

20

ns

311

RXDHLD

Hold of RXD after RXC high

5

ns

312

CRSSET

Setup of CRS high before RXC no longer low for first valid data sample

20

ns

313

SAMDLY

Delay of CRS internally recognized to first valid data sample (see Notes 16 and 17)

nominal 3 clk cycles

314

RXCHI

Pulse duration of RXC high

36

ns

315

RXCL0

Pulse duration of RXC low

36

ns

NOTES: 16. For valid frame synchronization one of the following data sequences must be received. Any other pattern will delay frame

synchronization until after the next CRS rising edge.

a)

0n (10)

11

where n is an integer and n is greater than or equal to 3

b)

10n (10)

11

17. If a previous frame or frame fragment completed without extra RXC clock cycles (XTRCVC = 0), then SAMDLY = 2 clock cycles.

CRS

RXC

RXD

312

314

311

315

313

310

Figure 23. Ethernet Timing of RCV Signals — Start Of Frame