Texas Instruments TMS380C26 User Manual

Page 40

TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL 1992–REVISED MARCH 1993

POST OFFICE BOX 1443

•

HOUSTON, TEXAS

77251–1443

40

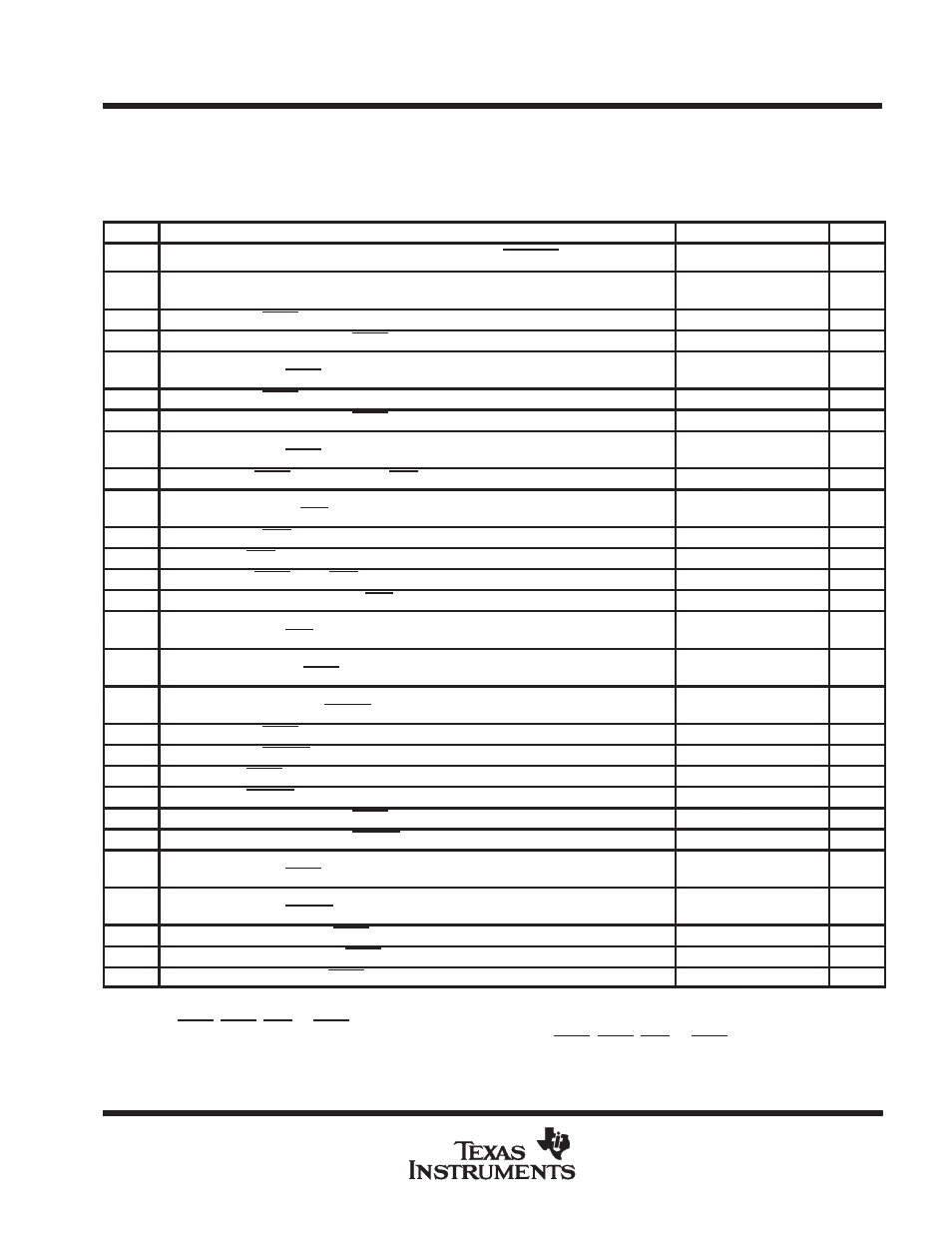

PARAMETER MEASUREMENT INFORMATION

memory bus timing: read cycle

t

M

is the cycle time of one-eighth of a local memory cycle (31.25 ns minimum)

NO.

PARAMETER

MIN

MAX

UNIT

32

Access time from address/enable valid on MAX0, MAX2, and MROMEN to valid data/parity

6tM – 23

ns

33

Access time from address valid on MAXPH, MAXPL, MADH0–MADH7, and MADL0–MADL7

to valid data/parity

6tM – 23

ns

35

Access time from MRAS low to valid data/parity

4.5tM – 21.5

ns

36

Hold time of valid data/parity after MRAS no longer low

0

ns

37†

Hold time of address high impedance on MAXPH, MAXPL, MADH0–MADH7 and

MADL0–MADL7 after MRAS high (see Note 13)

2tM –10.5

ns

38

Access time from MCAS low to valid data/parity

3tM –23

ns

39

Hold time of valid data/parity after MCAS no longer low

0

ns

40†

Hold time of address high impedance on MAXPH, MAXPL, MADH0–MADH7, and

MADL0–MADL7 after MCAS high (see Note 13)

2tM –13

ns

41

Delay time from MCAS no longer high to MOE low

tM +13

ns

42†

Setup time of address/status high impedance on MAXPH, MAXPL, MADL0–MADL7, and

MADH0–MADH7 before MOE no longer high

0

ns

43

Access time from MOE low to valid data/parity

2tM – 25

ns

44

Pulse duration MOE low

2tM – 9

ns

45

Delay time from MCAS low to MOE no longer low

3tM – 9

ns

46

Hold time of valid data/parity in after MOE no longer low

0

ns

47†

Hold time of address high impedance on MAXPH, MAXPL, MADH0–MADH7, and

MADL0–MADL7 after MOE high (see Note 13)

2tM – 15

ns

48†

Setup time of address/status high impedance on MAXPH, MAXPL, MADL0–MADL7, and

MADH0–MADH7, before MBEN no longer high

0

ns

48a†

Setup time of address/status high impedance on MAXPH, MAXPL, MADL0–MADL7, and

MADH0–MADH7 and before MBIAEN no longer high

0

ns

49

Access time from MBEN low to valid data/parity

2tM – 25

ns

49a

Access time from MBIAEN low to valid data/parity

2tM – 25

ns

50

Pulse duration MBEN low

2tM – 9

ns

50a

Pulse duration MBIAEN low

2tM – 9

ns

51

Hold time of valid data/parity after MBEN no longer low

0

ns

51a

Hold time of valid data/parity after MBIAEN no longer low

0

ns

52†

Hold time of address high impedance on MAXPH, MAXPL, MADH0–MADH7, and

MADL0–MADL7 after MBEN high (see Note 13)

2tM – 15

ns

52a†

Hold time of address high impedance on MAXPH, MAXPL, MADH0–MADH7, and

MADL0–MADL7 after MBIAEN high

2tM – 15

ns

53

Hold time of MDDIR high after MBEN high, read follows write cycle

1.5tM – 12

ns

54

Setup time of MDDIR low before MBEN no longer high

3tM – 9

ns

55

Hold time of MDDIR low after MBEN high, write follows read cycle

3tM – 12

ns

† This specification has been characterized to meet stated value.

NOTE 13: The data/parity that exists on the address lines will most likely achieve a high-impedance condition sometime later than the rising edge,

of MRAS, MCAS, MOE, or MBEN (between MIN and MAX of timing parameter 36) and will be a function of the memory being read.

Hence, the MIN time given represents the time from the rising edge of MRAS, MCAS, MOE, or MBEN to the beginning of the next

address, and does not represent the actual high-impedance period on the address bus.