Texas Instruments TMS380C26 User Manual

Page 42

TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL 1992–REVISED MARCH 1993

POST OFFICE BOX 1443

•

HOUSTON, TEXAS

77251–1443

42

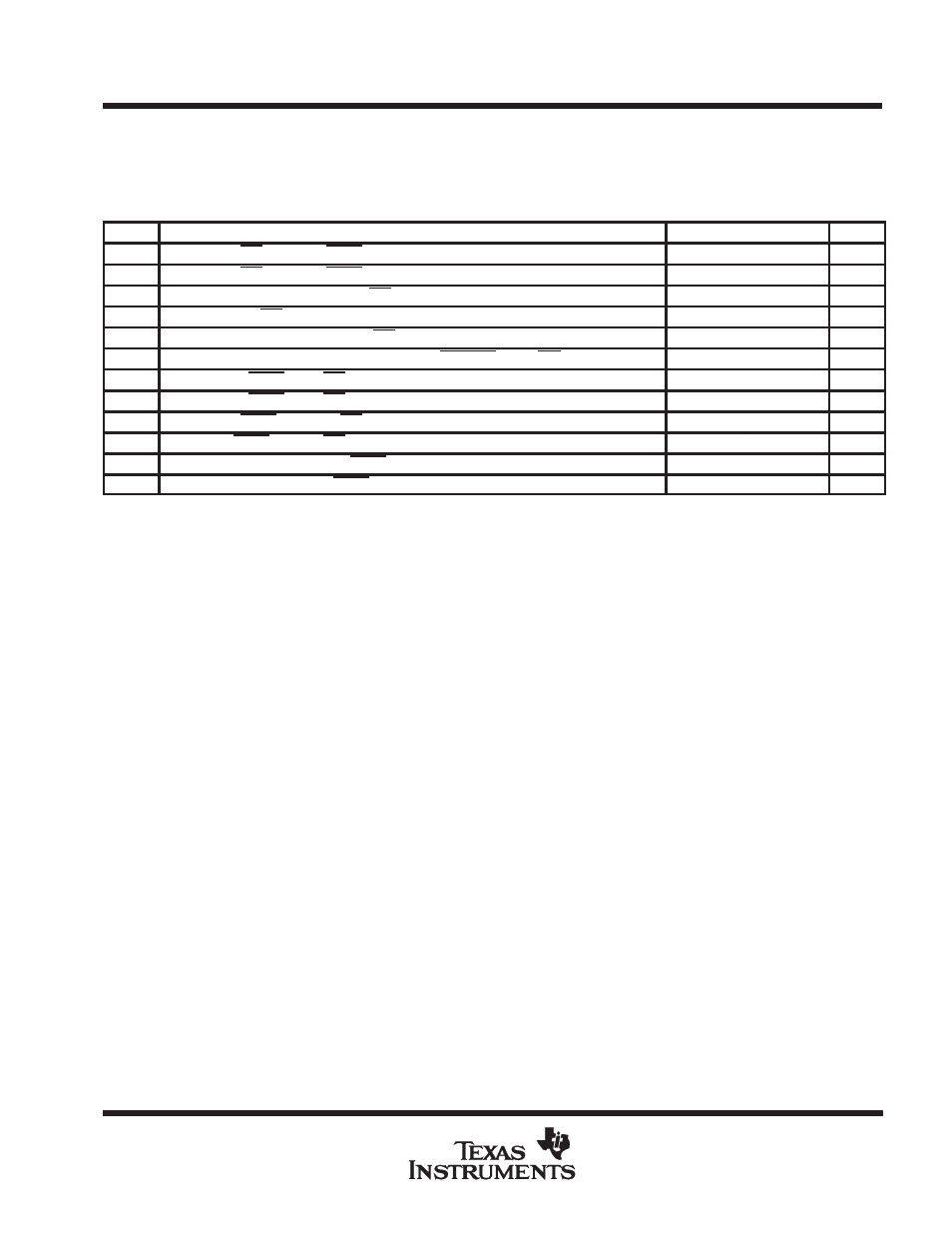

PARAMETER MEASUREMENT INFORMATION

memory bus timing: write cycle

t

M

is the cycle time of one-eighth of a local memory cycle (31.25 ns minimum)

NO.

PARAMETER

MIN

MAX

UNIT

58

Setup time of MW low before MRAS no longer low

1.5tM – 9

ns

60

Setup time of MW low before MCAS no longer low

1.5tM – 6.5

ns

63

Setup time of valid data/parity before MW no longer high

0.5tM –11.5

ns

64

Pulse duration of MW low

2.5tM – 9

ns

65

Hold time of data/parity out valid after MW high

0.5tM – 10.5

ns

66

Setup time of address valid on MAX0, MAX2, and MROMEN before MW no longer low

7tM –11.5

ns

67

Hold time from MRAS low to MW no longer low

5.5tM – 9

ns

69

Hold time from MCAS low to MW no longer low

4tM –11.5

ns

70

Setup time of MBEN low before MW no longer high

1.5tM – 13.5

ns

71

Hold time of MBEN low after MW high

0.5tM – 6.5

ns

72

Setup time of MDDIR high before MBEN no longer high

2tM – 9

ns

73

Hold time of MDDIR high after MBEN high

1.5tM – 12

ns