Renesas RJJ10J1643-0101 User Manual

Page 45

Rev.1.01 2007.02.16

RJJ10J1643-0101

43

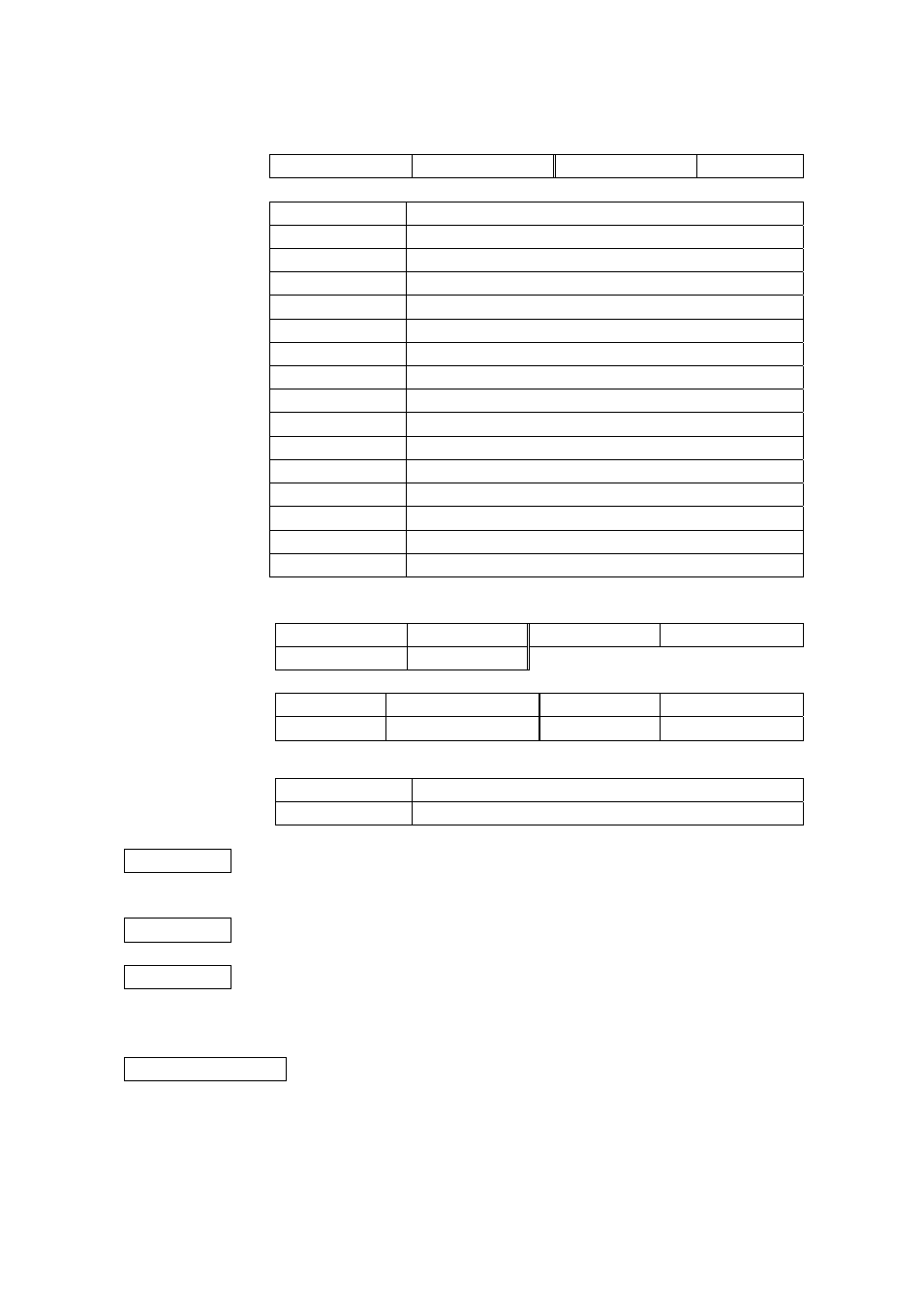

RAPI_COM1 UART0

RAPI_COM2 UART1

For interrupt settings, the following values can set.

RAPI_INT_TX_DIS

Transmit interrupt disabled

RAPI_INT_TX_LV_1

Transmit interrupt priority level 1

RAPI_INT_TX_LV_2

Transmit interrupt priority level 2

RAPI_INT_TX_LV_3

Transmit interrupt priority level 3

RAPI_INT_TX_LV_4

Transmit interrupt priority level 4

RAPI_INT_TX_LV_5

Transmit interrupt priority level 5

RAPI_INT_TX_LV_6

Transmit interrupt priority level 6

RAPI_INT_TX_LV_7

Transmit interrupt priority level 7

RAPI_INT_RX_DIS

Receive interrupt disabled

RAPI_INT_RX_LV_1

Receive interrupt priority level 1

RAPI_INT_RX_LV_2

Receive interrupt priority level 2

RAPI_INT_RX_LV_3

Receive interrupt priority level 3

RAPI_INT_RX_LV_4

Receive interrupt priority level 4

RAPI_INT_RX_LV_5

Receive interrupt priority level 5

RAPI_INT_RX_LV_6

Receive interrupt priority level 6

RAPI_INT_RX_LV_7

Receive interrupt priority level 7

(H8/300H)

RAPI_COM1

SCI3 channel 1

RAPI_COM2

SCI3 channel 2

RAPI_COM3

SCI3 channel 3

For interrupt settings, the following values can set.

RAPI_INT_TX_DIS

Transmit interrupt disabled

RAPI_INT_TX_ENA

Transmit interrupt enabled

RAPI_INT_RX_DIS

Receive interrupt disabled

RAPI_INT_RX_ENA

Receive interrupt enabled

For the CPUs that have an interrupt control register, following values can be set to

specify interrupt priority, in addition to ordinary interrupt settings.

RAPI_INT_LV_0

Transmit/Receive interrupt priority level0

RAPI_INT_LV_1

Transmit/Receive interrupt priority level1

Return value

If the serial port specification is incorrect, RAPI_FALSE is returned; otherwise,

RAPI_TRUE is returned.

Functionality

Serial I/O

Remark

•

The specifiable serial ports differ with each CPU used.

•

If an undefined value is specified in the argument, operation of the API cannot be

guaranteed.

Program example

#include ”rapi_sif_r8c_13.h”