Memory, Ddr3, Memory –42 – Altera Stratix V Advanced Systems Development Board User Manual

Page 52: Ddr3 –42

2–42

Chapter 2: Board Components

Memory

Stratix V Advanced Systems Development Board

January 2014

Altera Corporation

Reference Manual

Memory

This section describes the development board memory interface support, signal

names, types, and connectivity relative to the Stratix V GX FPGA devices. The board

has the following memory interfaces:

■

DDR3

■

QDRII+

■

MoSYS SRAM

■

Flash

f

For more information about the memory interfaces, refer to the

page of the Altera website.

DDR3

Each FPGA device on the development board supports the following interfaces for

very high-speed sequential memory access:

■

FPGA1—two 64-bit and two 32-bit interfaces

■

64-bit data bus consists of four x16 DDR3 SDRAM device

■

32-bit data bus consists of two x16 DDR3 SDRAM device

■

FPGA2—two 64-bit and two 32-bit interfaces

■

64-bit data bus consists of four x16 DDR3 SDRAM device

■

32-bit data bus consists of two x16 DDR3 SDRAM device

The DDR3 devices on this board have a target speed of 933 MHz DDR for a total

theoretical bandwidth of over 716.5 Gbps. These devices run at a minimum frequency

of 300 MHz.

lists the DDR3 devices pin assignments, signal names, and functions for

FPGA1.

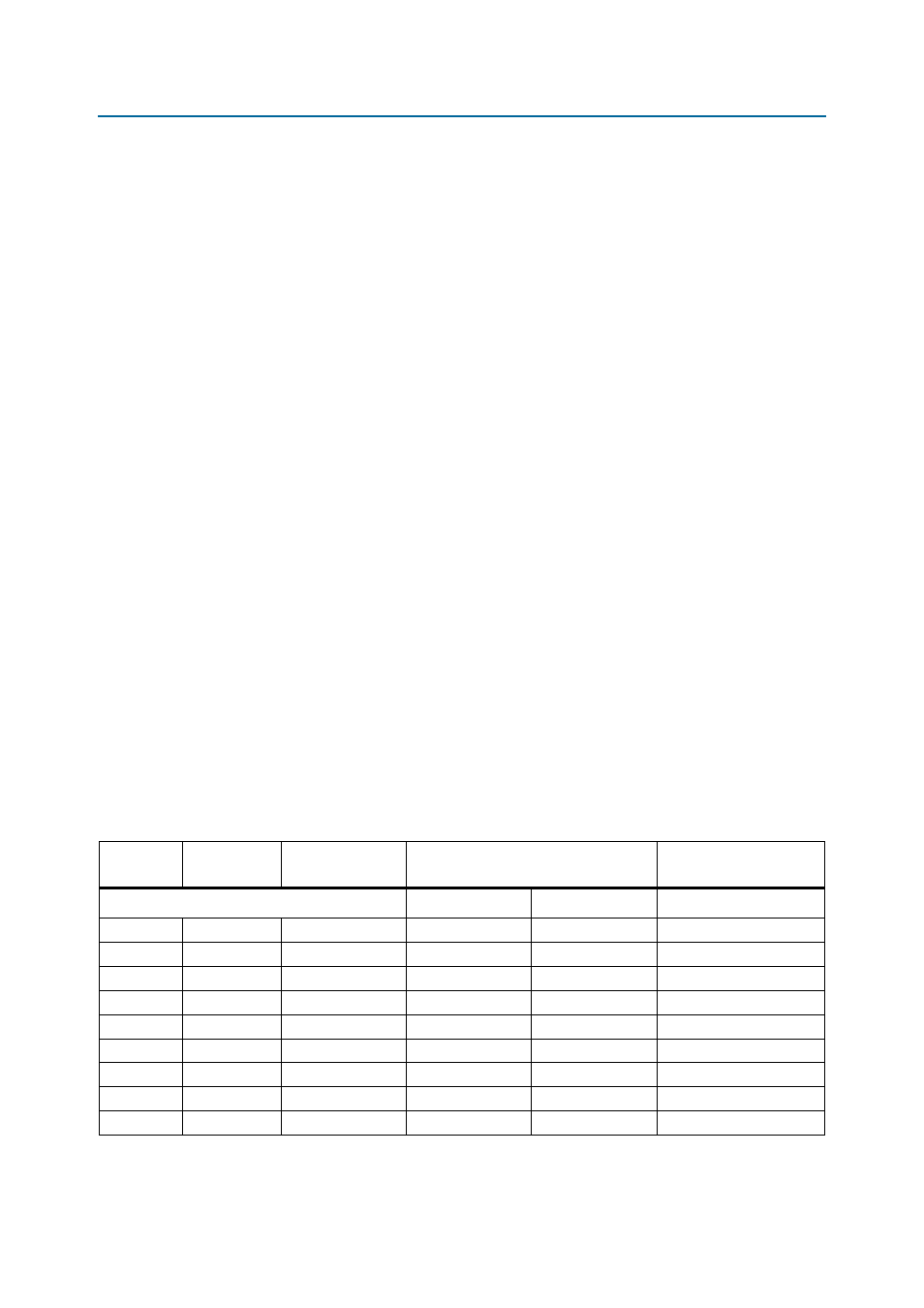

Table 2–23. FPGA1 DDR3 Devices Pin Assignments, Schematic Signal Names, and Functions (Part 1 of 7)

Board

Reference

Schematic

Signal Name

I/O Standard

Stratix V GX FPGA1 Device Pin Number

Description

DDR3A_

/ DDR3C_ (x32 bit interface)

DDR3A

DDR3C

N3

A0

1.5-V SSTL Class I

BC20

G28

Address bus

P7

A1

1.5-V SSTL Class I

AP21

A26

Address bus

P3

A2

1.5-V SSTL Class I

AR22

C27

Address bus

N2

A3

1.5-V SSTL Class I

BA22

T27

Address bus

P8

A4

1.5-V SSTL Class I

AY21

G26

Address bus

P2

A5

1.5-V SSTL Class I

AY22

K28

Address bus

R8

A6

1.5-V SSTL Class I

AV20

H27

Address bus

R2

A7

1.5-V SSTL Class I

AW21

J28

Address bus

T8

A8

1.5-V SSTL Class I

AU22

F26

Address bus