Altera Stratix V Advanced Systems Development Board User Manual

Page 33

Chapter 2: Board Components

2–23

Clock Circuitry

January 2014

Altera Corporation

Stratix V Advanced Systems Development Board

Reference Manual

lists the oscillators, its I/O standard, and voltages required for the

development board.

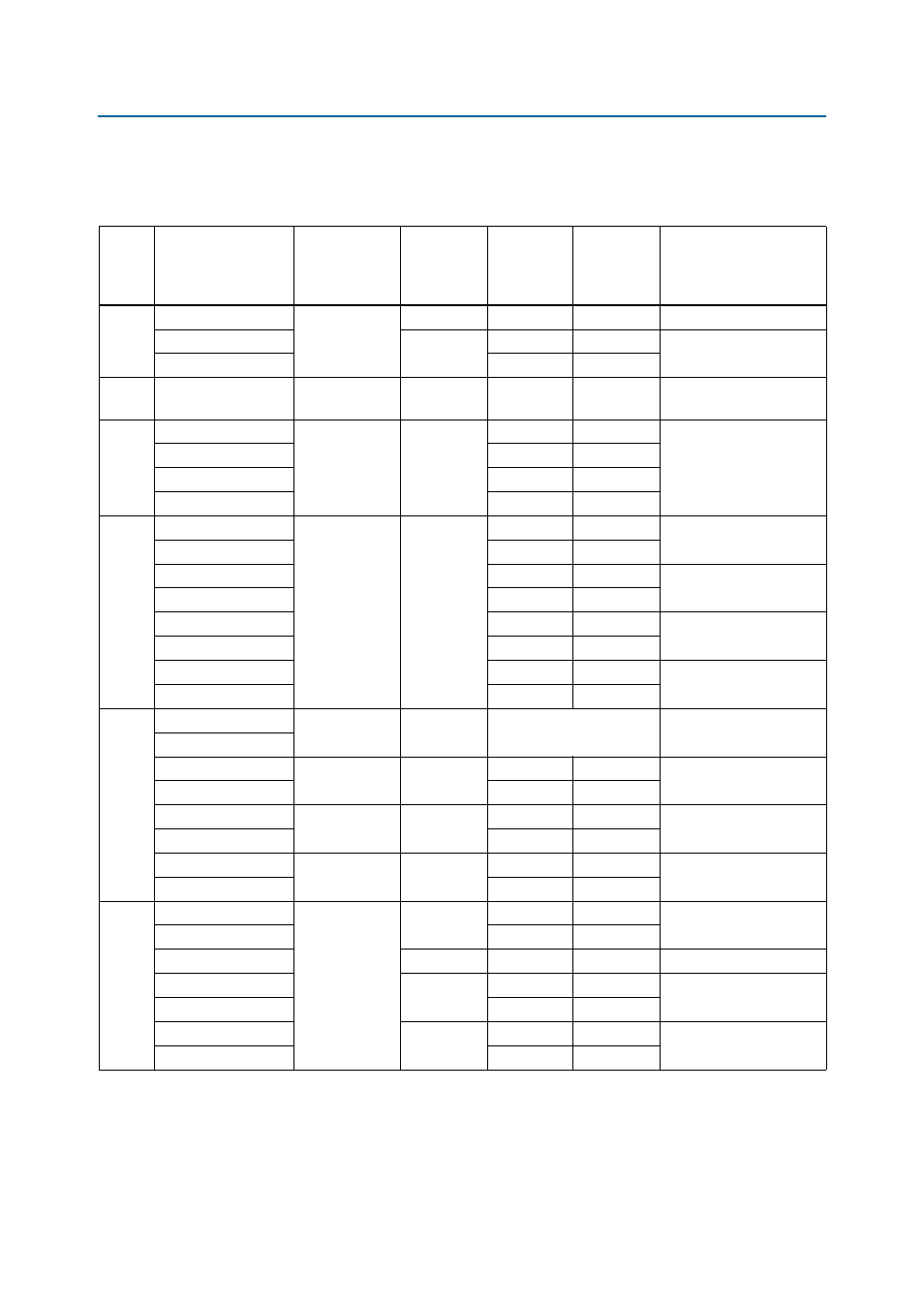

Table 2–12. On-Board Oscillators (Part 1 of 2)

Source

Schematic Signal

Name

Frequency

I/O Standard

Stratix V GX

FPGA1

Device Pin

Number

Stratix V GX

FPGA2

Device Pin

Number

Application

X2

MV_CLK_50

50.000 MHz

1.8-V CMOS

—

—

MAX V System Controller

SVB_CLK_50

1.5-V CMOS

—

R25

Nios II

SVA_CLK_50

R25

—

X3

CLK_CONFIG

100.000 MHz

2.5-V CMOS

—

—

MAX V Fast FPGA

configuration

X1

SVA_CLK_125_P

125.000 MHz

LVDS

(fan out

buffer)

AW35

—

Nios II

SVA_CLK_125_N

AY36

—

SVB_CLK_125_P

—

AW35

SVB_CLK_125_N

—

AY36

U50

REFCLKA_QL3_P

100.000 MHz

(BUFFER_CLKI

N_P/N or SMA)

LVDS

(fan out

buffer)

T38

—

FMC

REFCLKA_QL3_N

T39

—

SVA_CLK_P

AP10

—

General purpose

SVA_CLK_N

AR10

—

REFCLKB_QL3_P

—

V39

HSMC

REFCLKB_QL3_N

—

V40

SVB_CLK_P

—

AP10

General purpose

SVB_CLK_N

—

AR10

U91

BUFFER_CLKIN_P

100.000 MHz

LVDS

Buffer Input (U50)

Refer to board reference

U50

BUFFER_CLKIN_N

REFCLKA_QL2_P

644.53125 MHz

LVDS

Y38

—

FMC

REFCLKA_QL2_N

Y39

—

REFCLKA_QL1_P

644.53125 MHz

LVDS

AF38

—

FMC

REFCLKA_QL1_N

AF39

—

REFCLKA_QL0_P

100.000 MHz

LVDS

AH39

—

PCI Express

REFCLKA_QL0_N

AH40

—

U82

CLKINTOPA_DDR3_P

100.000 MHz

(Default)

LVDS

N25 —

DDR3 top edge

CLKINTOPA_DDR3_N

M25 —

CLKINTOPA_QDR2

1.8-V CMOS

B37

—

QDRII+ top edge

CLKINBOTA_QDR2_P

LVDS

BB18 —

QDRII+ bottom edge

CLKINBOTA_QDR2_N

BB17 —

CLKINBOTA_DDR3_P

LVDS

BB33 —

DDR3 bottom edge

CLKINBOTA_DDR3_N

BC34

—