Off-board clock input/output, Off-board clock input/output –24 – Altera Stratix V Advanced Systems Development Board User Manual

Page 34

2–24

Chapter 2: Board Components

Clock Circuitry

Stratix V Advanced Systems Development Board

January 2014

Altera Corporation

Reference Manual

Off-Board Clock Input/Output

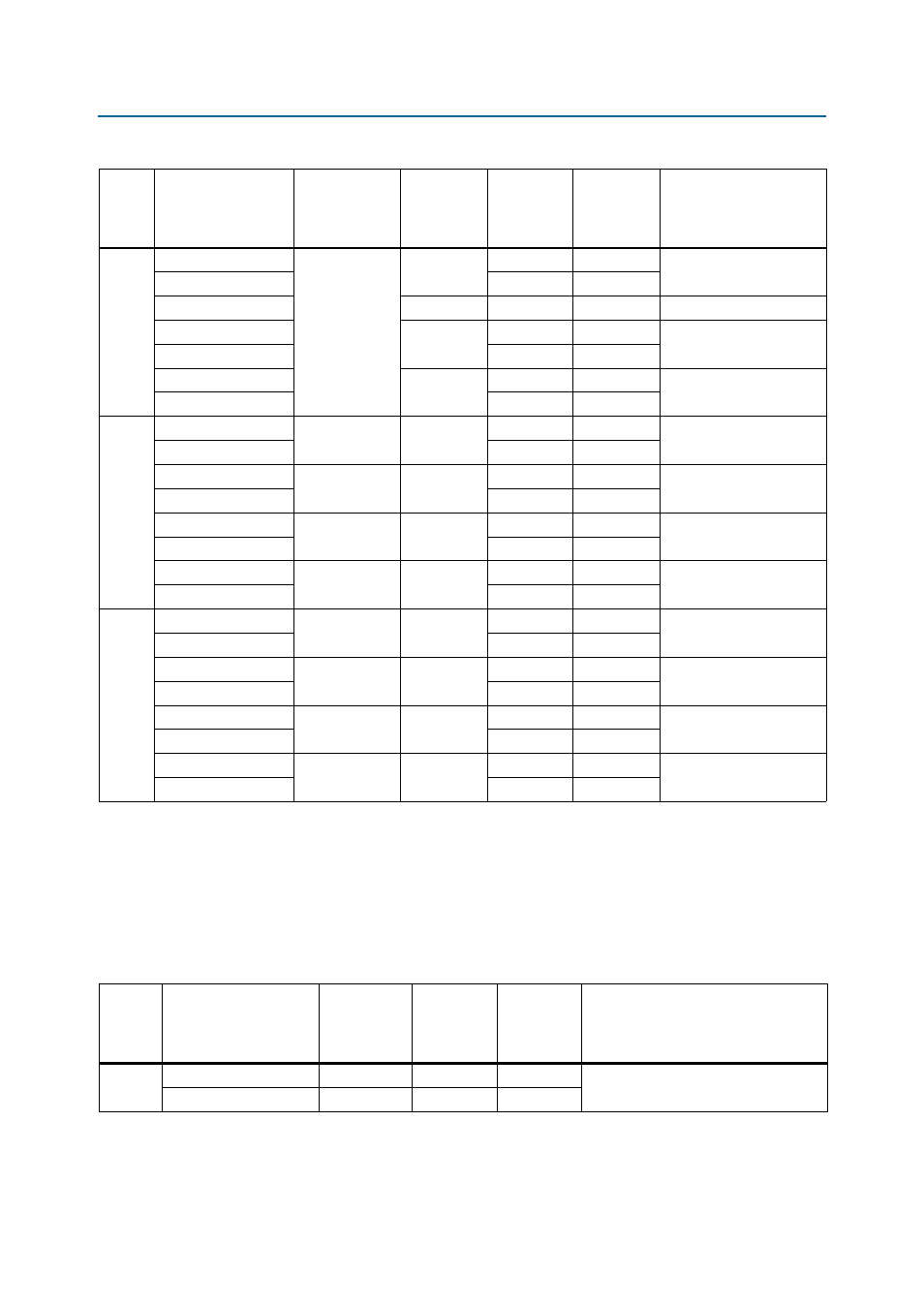

The development board has input and output clocks which can be driven onto the

board. The output clocks can be programmed to different levels and I/O standards

according to the FPGA device’s specification.

lists the clock inputs for the development board.

U100

CLKINTOPB_DDR3_P

100.000 MHz

(Default)

LVDS

—

N25

DDR3 top edge

CLKINTOPB_DDR3_N

—

M25

CLKINTOPB_QDR2

1.8-V CMOS

—

B37

QDRII+ top edge

CLKINBOTB_QDR2_P

LVDS

—

BB18

QDRII+ bottom edge

CLKINBOTB_QDR2_N

—

BB17

CLKINBOTB_DDR3_P

LVDS

—

BB33

DDR3 bottom edge

CLKINBOTB_DDR3_N

—

BC34

U53

MOSYS1_REFCLK_P

206.250 MHz

LVDS

—

—

MoSYS MSR576 (U4)

reference clock

MOSYS1_REFCLK_N

—

—

REFCLKA_QR2_P

625.000 MHz

LVDS

Y7

—

Chip-to-chip

REFCLKA_QR2_N

Y6

—

REFCLKA_QR0_P

206.250 MHz

LVDS

AK7

—

MoSYS MSR576

REFCLKA_QR0_N

AK6

—

REFCLKB_QR0_P

625.000 MHz

LVDS

—

AK7

Chip-to-chip

REFCLKB_QR0_N

—

AK6

U95

MOSYS2_REFCLK_P

206.250 MHz

LVDS

—

—

MoSYS MSR576 (U14)

reference clock

MOSYS2_REFCLK_N

—

—

REFCLKB_QR2_P

206.250 MHz

LVDS

—

AB6

MoSYS MSR576

REFCLKB_QR2_N

—

AB5

REFCLKB_QL2_P

706.250 MHz

LVDS

—

AB39

HSMC

REFCLKB_QL2_N

—

AB40

REFCLKB_QL0_P

100.000 MHz

LVDS

—

AH39

Chip-to-chip

REFCLKB_QL0_N

—

AH40

Table 2–12. On-Board Oscillators (Part 2 of 2)

Source

Schematic Signal

Name

Frequency

I/O Standard

Stratix V GX

FPGA1

Device Pin

Number

Stratix V GX

FPGA2

Device Pin

Number

Application

Table 2–13. Off-Board Clock Inputs (Part 1 of 2)

Source

Schematic Signal Name

I/O Standard

Stratix V GX

FPGA1

Device Pin

Number

Stratix V GX

FPGA2

Device Pin

Number

Description

SMA

SMA_CLKIN_P

LVDS

—

—

Input to LVDS fan out buffer (U50)

SMA_CLKIN_N

LVDS

—

—