Altera Stratix V Advanced Systems Development Board User Manual

Page 25

Chapter 2: Board Components

2–15

Configuration, Status, and Setup Elements

January 2014

Altera Corporation

Stratix V Advanced Systems Development Board

Reference Manual

1

By default, the on-board USB-Blaster II clocks TCK at 24 MHz. For the on-board

USB-Blaster II to function correctly, you must set the Quartus II clock constraint on the

altera_reserved_tck

input signal to 24 MHz.

System Console USB Interface

The System Console USB interface is a fast parallel interface available on FPGA1.

Together with the soft logic supplied by Altera, this interface provides a System

Console master for debug access.

The System Console controls the debug master via signals shown in

fast access to an Avalon

®

Memory-Mapped (Avalon-MM) master bus that the Qsys

system integration tool generates.

f

For more information about the System Console, re

3 of the Quartus II Handbook.

lists the System Console USB interface pin connections relative to the FPGA.

CFI Flash Programming

Flash programming is possible using the pre-built PFL design included in the

development kit to write configuration data to the CFI flash. The development board

implements the Altera PFL megafunction for flash programming. The PFL

megafunction is a block of logic that is programmed into an Altera programmable

logic device, in this case, the MAX V CPLD. The PFL functions as a utility for writing

to a compatible flash device.

This pre-built design contains the PFL megafunction that allows you to write either

page 0, page 1, or other areas of flash over the on-board USB-Blaster II interface using

the Quartus II software.

1

Use this method to restore the development board to its factory default settings.

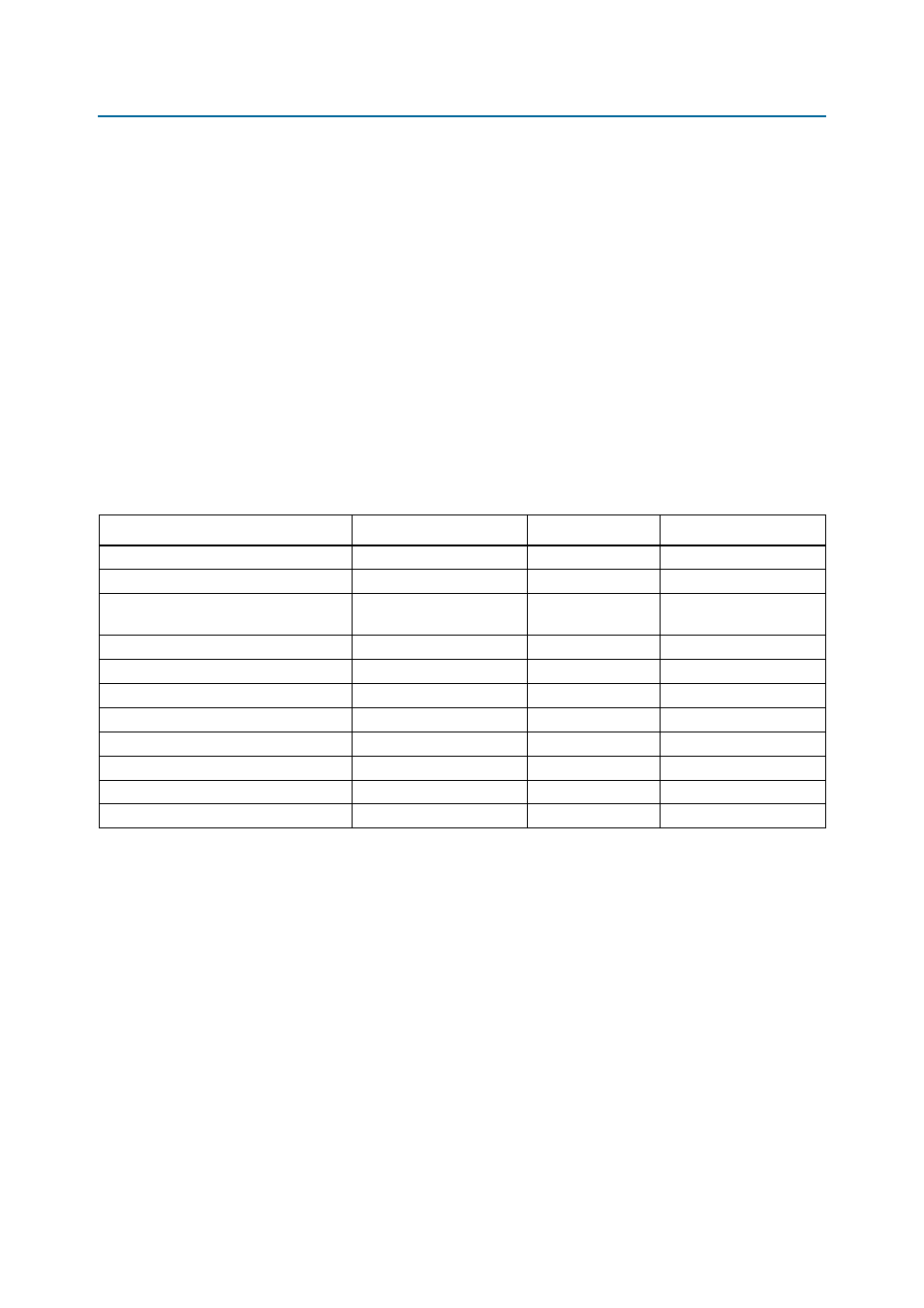

Table 2–6. System Console USB Interface Pin Connections

Stratix V GX FPGA1 (U29) Pin Number

Schematic Signal Name

Direction

Note

BC8

usb_clk

input

48 MHz

BD34

usb_resetn

input

—

BA15, AJ13, AR16, AH13, BD14, AF17,

BC14, AP13

usb_data[7:0]

bidirectional

BA15 (MSB), AP13 (LSB)

AW33

usb_full

output

—

AU35

usb_empty

output

—

AJ29

usb_wrn

input

—

AT33

usb_rdn

input

—

AV34

usb_oen

input

—

AF13, BD10

usb_addr[1:0]

bidirectional

Reserved

BD35

usb_scl

bidirectional

—

BA31

usb_sda

bidirectional

—