Altera Stratix V Advanced Systems Development Board User Manual

Page 20

2–10

Chapter 2: Board Components

MAX V CPLD System Controller

Stratix V Advanced Systems Development Board

January 2014

Altera Corporation

Reference Manual

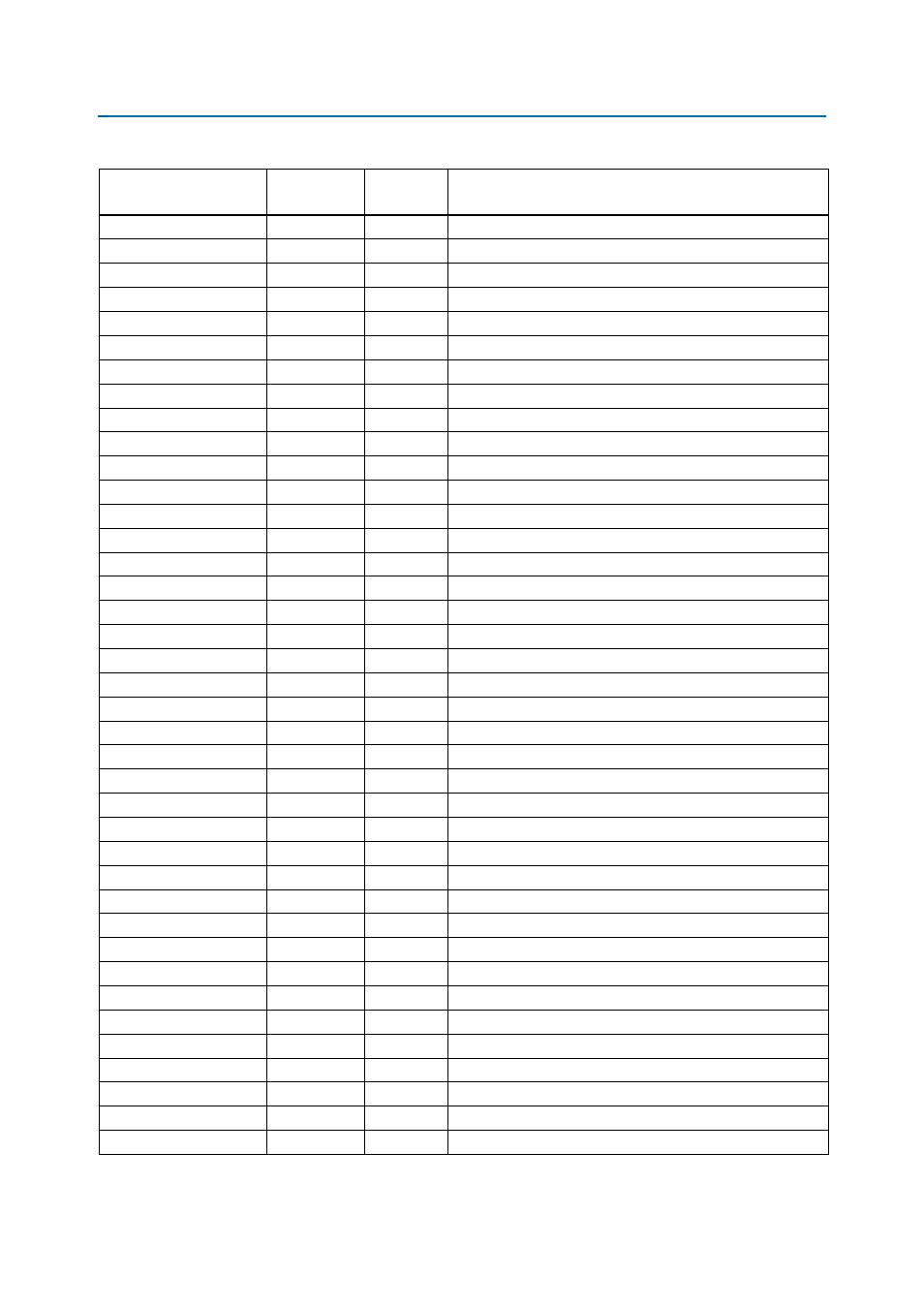

FPGA1_OVERTEMP

A11

2.5-V

FPGA1 temperature monitor fan enable

FPGA1_OVERTEMPN

D7

2.5-V

FPGA1 temperature monitor over-temperature indicator LED

FPGA1_PR_DONE

N9

1.5-V

FPGA1 partial reconfiguration done

FPGA1_PR_ERROR

M10

1.5-V

FPGA1 partial reconfiguration error

FPGA1_PR_READY

M8

1.5-V

FPGA1 partial reconfiguration ready

FPGA1_PR_REQUEST

R3

1.5-V

FPGA1 partial reconfiguration request

FPGA2_CONF_DONE

P2

2.5-V

FPGA2 configuration done

FPGA2_CPU_RESETN

N3

2.5-V

FPGA2 reset

FPGA2_CVP_CONFDONE

T2

2.5-V

FPGA2 configuration via protocol done

FPGA2_DCLK

K5

2.5-V

FPGA2 configuration clock

FPGA2_FPP

B14

2.5-V

Configure FPGA2 via FPP at power up

FPGA2_MSEL0

G1

2.5-V

DIP switch for FPGA2 mode select 0

FPGA2_MSEL1

L1

2.5-V

DIP switch for FPGA2 mode select 1

FPGA2_MSEL2

J1

2.5-V

DIP switch for FPGA2 mode select 2

FPGA2_MSEL3

N1

2.5-V

FPGA2 mode select 3

FPGA2_MSEL4

M1

2.5-V

FPGA2 mode select 4

FPGA2_NCE

K1

2.5-V

FPGA2 chip enable

FPGA2_NCEO

M4

2.5-V

FPGA2 chip enable output

FPGA2_NCONFIG

L5

2.5-V

FPGA2 configuration active

FPGA2_NSTATUS

H1

2.5-V

FPGA2 configuration ready status

FPGA2_OVERTEMP

D10

2.5-V

FPGA2 temperature monitor fan enable

FPGA2_OVERTEMPN

E10

2.5-V

FPGA2 temperature monitor over-temperature indicator LED

FPGA2_PR_DONE

R6

1.5-V

FPGA2 partial reconfiguration done

FPGA2_PR_ERROR

R1

1.5-V

FPGA2 partial reconfiguration error

FPGA2_PR_READY

T5

1.5-V

FPGA2 partial reconfiguration ready

FPGA2_PR_REQUEST

R5

1.5-V

FPGA2 partial reconfiguration request

FPGA_CONFIG_D0

D3

2.5-V

FPGA configuration data

FPGA_CONFIG_D1

C2

2.5-V

FPGA configuration data

FPGA_CONFIG_D2

C3

2.5-V

FPGA configuration data

FPGA_CONFIG_D3

D1

2.5-V

FPGA configuration data

FPGA_CONFIG_D4

D2

2.5-V

FPGA configuration data

FPGA_CONFIG_D5

E4

2.5-V

FPGA configuration data

FPGA_CONFIG_D6

D4

2.5-V

FPGA configuration data

FPGA_CONFIG_D7

E5

2.5-V

FPGA configuration data

HSMC_PRSNTN

B8

2.5-V

HSMC port present

JTAG_5M2210_TDI

L6

2.5-V

MAX V JTAG data in

JTAG_5M2210_TDO

M5

2.5-V

MAX V JTAG data out

JTAG_TCK

P3

2.5-V

MAX V JTAG clock

JTAG_TMS

N4

2.5-V

MAX V JTAG TMS

Table 2–4. MAX V CPLD System Controller Device Pin-Out (Part 3 of 5)

Schematic Signal Name

MAX V CPLD

Pin Number

I/O

Standard

Description