Board settings dip switch, Jtag control dip switch, Pci express control dip switch – Altera Stratix V Advanced Systems Development Board User Manual

Page 30

2–20

Chapter 2: Board Components

Configuration, Status, and Setup Elements

Stratix V Advanced Systems Development Board

January 2014

Altera Corporation

Reference Manual

Board Settings DIP Switch

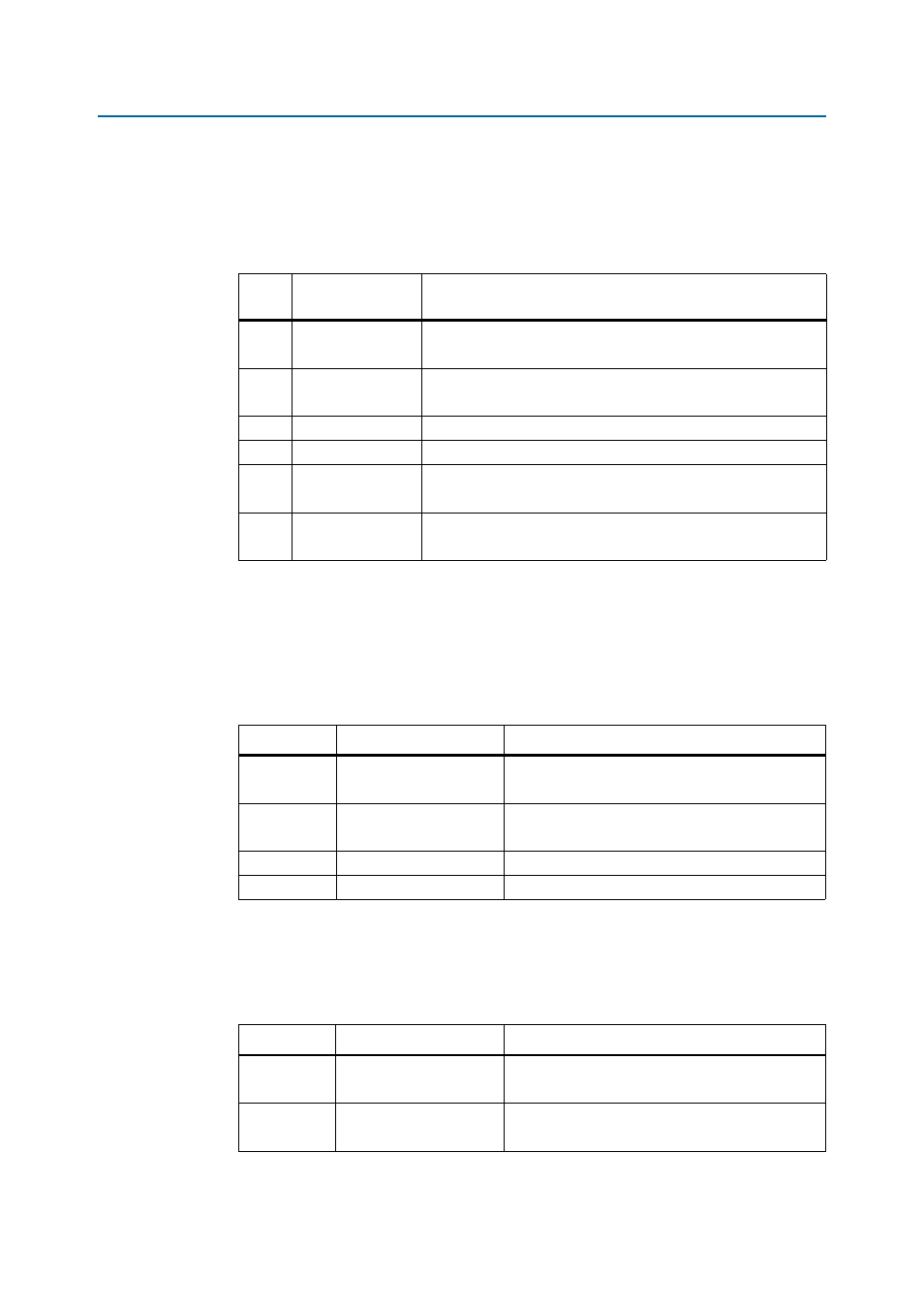

The board settings DIP switch (SW4) controls various features specific to the board

and the MAX V CPLD System Controller logic design.

Table 2–9

lists the switch

controls and descriptions.

JTAG Control DIP Switch

The JTAG control DIP switch (SW7) provides you an option to either remove or

include devices in the active JTAG chain. However, both Stratix V GX FPGA devices

are always in the JTAG chain.

Table 2–10

shows the switch controls and its

descriptions.

PCI Express Control DIP Switch

The PCI Express control DIP switch (SW8) can enable or disable different

configurations.

Table 2–11

shows the switch controls and descriptions.

Table 2–9. Board Settings DIP Switch Controls

Switch

(SW4)

Schematic Signal

Name

Description

1

CLK_SEL

ON: SMA input clock select.

OFF: Programmable oscillator input clock select (default 100 MHz).

2

CLK_ENABLE

ON: Disable on-board oscillator.

OFF: Enable on-board oscillator.

3

EXTRA1

Unused

4

EXTRA0

Unused

5

FPGA2_FPP

ON: Load factory design from flash page 1 to FPGA2 at power up.

OFF: No design is configured to FPGA2 using FPP x8.

6

FPGA1_FPP

ON: Load factory design from flash page 0 to FPGA1 at power up.

OFF: No design is configured to FPGA1 using FPP x8.

Table 2–10. JTAG Control DIP Switch Controls

Switch (SW7)

Schematic Signal Name

Description

1

HSMC_JTAG_EN

ON: Bypass HSMC.

OFF: HSMC in-chain.

2

FMC_JTAG_EN

ON: Bypass FMC.

OFF: FMC in-chain.

3

—

Unused

4

—

Unused

Table 2–11. PCI Express Control DIP Switch Controls (Part 1 of 2)

Switch (SW8)

Schematic Signal Name

Description

1

PCIE_PRSNT2n_x1

ON: Enable x1 presence detect

OFF: Disable x1 presence detect

2

PCIE_PRSNT2n_x4

ON: Enable x4 presence detect

OFF: Disable x4 presence detect