Clock circuitry, On-board oscillators, Clock circuitry –22 – Altera Stratix V Advanced Systems Development Board User Manual

Page 32: On-board oscillators –22

2–22

Chapter 2: Board Components

Clock Circuitry

Stratix V Advanced Systems Development Board

January 2014

Altera Corporation

Reference Manual

Clock Circuitry

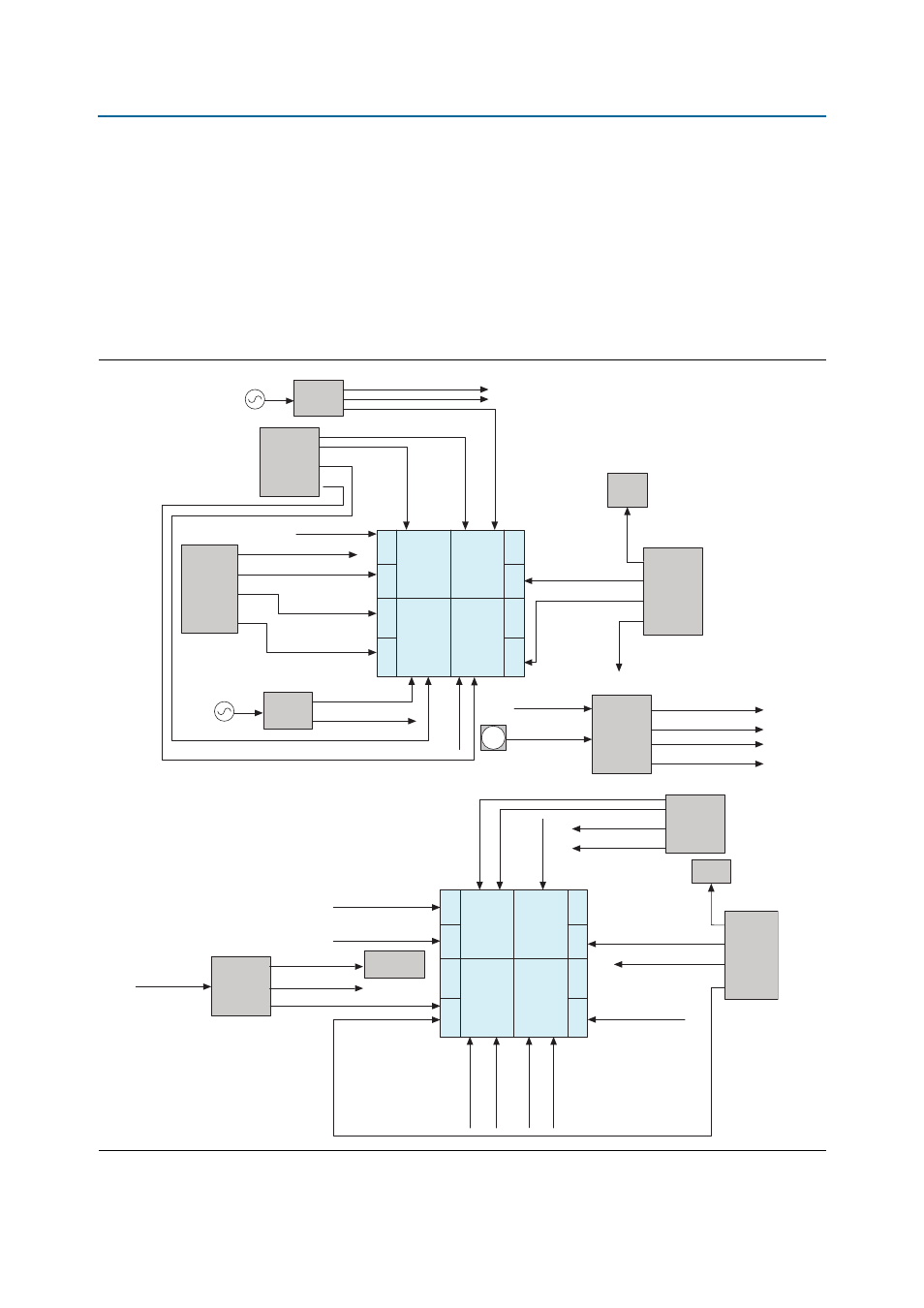

This section describes the board's clock inputs and outputs.

On-Board Oscillators

The development board includes a 50-MHz, 100-MHz, and 125-MHz programmable

oscillators.

shows the default frequencies of all external clocks going to the

Stratix V Advanced Systems development board.

Figure 2–5. Stratix V Advanced Systems Development Board External Clock Inputs and Default Frequencies

BUFFER_CLKIN_P/N

SMA_CLKIN

Reference

Clock Input

SMA

Buffer

IDT5T9306

100 MHz Default

REFCLKA_QL3_P/N (FMC)

SVA_CLK_P/N

REFCLKB_QL3_P/N (HSMC)

SVB_CLK_P/N

CLKINTOPA_QDR2_CMOS, 100 MHz

CLKINTOPA_DDR3_P/N, 100 MHz

SVA_CLK_50

MV_CLK_50

SVB_CLK_50

SL18860

Buffer

50 M

Si5338

100 MHz

Default

BUFFER_CLKIN_P/N

100 MHz

REFCLKA_QL2_P/N (FMC)

644.53125 MHz

REFCLKA_QL1_P/N (SFP+)

644.53125 MHz

REFCLKA_QL0_P/N (PCIe)

100 MHz

CLK3

CLK2

CLK1

CLK0

Si5338

REFCLKA_QL3_P/N (FMC)

QL3

QL2

QL1

QL0

QR3

QR2

QR1

QR0

B8

B7

B3

B4

Stratix V GX

FPGA1

SV

A_CLK_P/N

SVA_CLK_125_P/N

SVB_CLK_125_P/N

CLKINBOTA_QDR2_P/N, 100 MHz

CLKINBOTA_DDR3_P/N, 100 MHz

125 M

Buffer

Si5330

MoSys

MOSYS1_CLK_P/N

206.25 MHz

REFCLKA_QR2_P/N (C2C)

625 MHz

CLK3

CLK2

CLK1

CLK0

Si5338

REFCLKA_QR0_P/N (MoSys)

206.25 MHz

REFCLKB_QR0_P/N (C2C)

625 MHz

QL3

QL2

QL1

QL0

QR3

QR2

QR1

QR0

B8

B7

B3

B4

Stratix V GX

FPGA2

CLKINT

O

PB_QDR2_CMOS

SVB_CLK_50_P/N

CLKINT

O

PB_DDR3_P/N

CLKINBOTB_QDR2_P/N

CLKINBOTB_DDR3_P/N

Si5338

100 MHz

Default

PLX_PCIE_REFCLK_P/N

SVA_PCIE_REFCLK_P/N

SVB_PCIE_REFCLK_P/N

PCIe

Buffer

Si53154

REFCLKB_QL3_P/N (HSMC)

REFCLKB_QL2_P/N (HSMC)

REFCLKB_QL0_P/N (PCIe)

100 MHz

PCIE_REFCLK_P/N

SVB_CLK_125_P/N

CLKINBO

TB_DDR3_P/N

SVB_CLK_P/N

CLKINBO

TB_QDR2_P/N

REFCLKB_QR2_P/N (MoSys)

206.25 MHz

MOSYS2_CLK_P/N

206.25 MHz

CLK3

CLK2

CLK1

CLK0

Si5338

REFCLKB_QL2_P/N (HSMC)

706.25 MHz

REFCLKB_QR0_P/N (C2C)

MoSys

PLX PCIe Switch

PEX8747