Get_timing_node_info, Usage, Options – Altera Quartus II Scripting User Manual

Page 154: Description, Get_timing_node_info –24

3–24

Chapter 3: Tcl Packages & Commands

advanced_timing

Quartus II Scripting Reference Manual

© July 2013

Altera Corporation

get_timing_node_info

Usage

get_timing_node_info -info

Options

-info

Description

Returns the requested type of information for the specified timing node.

Available information types include the following:

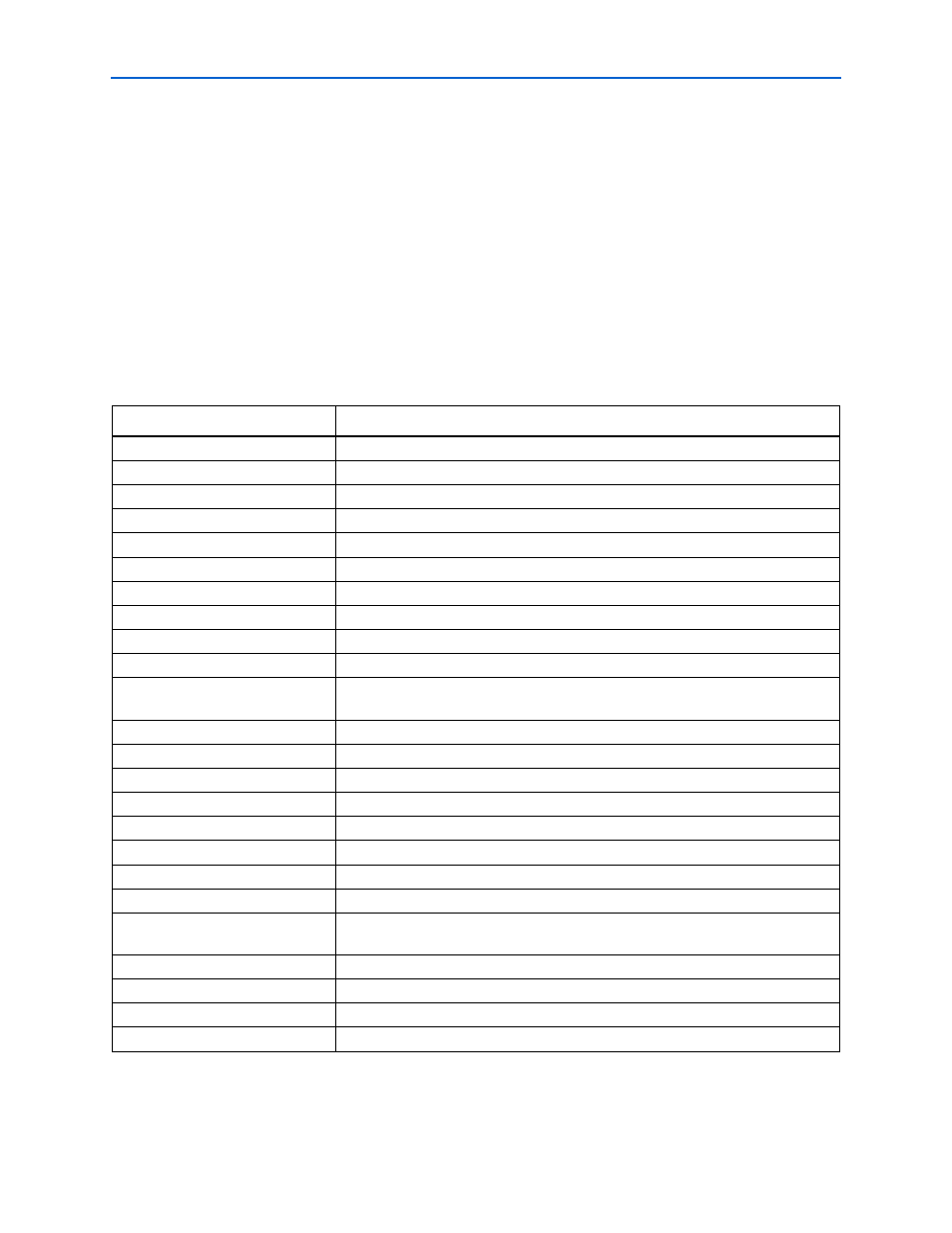

Information Type

Description

name

Signal name.

type

Type of node (reg, clk, pin, comb).

tsu

For a register, returns micro tsu.

th

For a register, returns micro th.

tco

For a register, returns micro tco.

location

Atom location in device.

is_loop

Detects whether the node is part of a strongly connected component.

is_clock_inverted

Detects whether a register is clocked by an inverted clock.

slack

Worst case slack of the node (Available after calling "compute_slack_on_edges")

delay

Delay of the node (if any).

is_tan_generated

Detects whether the Timing Analyzer (quartus_tan) synthesized the name of the

node.

is_lvds_channel

Detects whether node is part of an LVDS circuit.

wysiwyg_port_type

Atom's oterm type.

atom_oport

Corresponding atom's oterm (if any).

synch_edges

Synch edges.

asynch_edges

Asynch edges.

clock_edges

Clock edges.

fanout_edges

Fanout edges.

clock_info

Clock information.

internal_location

Internal pin location (IOC_ instead of Pin_). Works only for Stratix and newer device

families.

clock_latency

For a clock get the early and late clock latency values

is_pll_out

Detects whether the node is a PLL clock output

is_clock_pin

Detects whether the node is a clock pin

phase_only

Phase shift independent of offset for a clock