Root port tlp data registers, Root port tlp data registers -29 – Altera Arria 10 Avalon-MM User Manual

Page 95

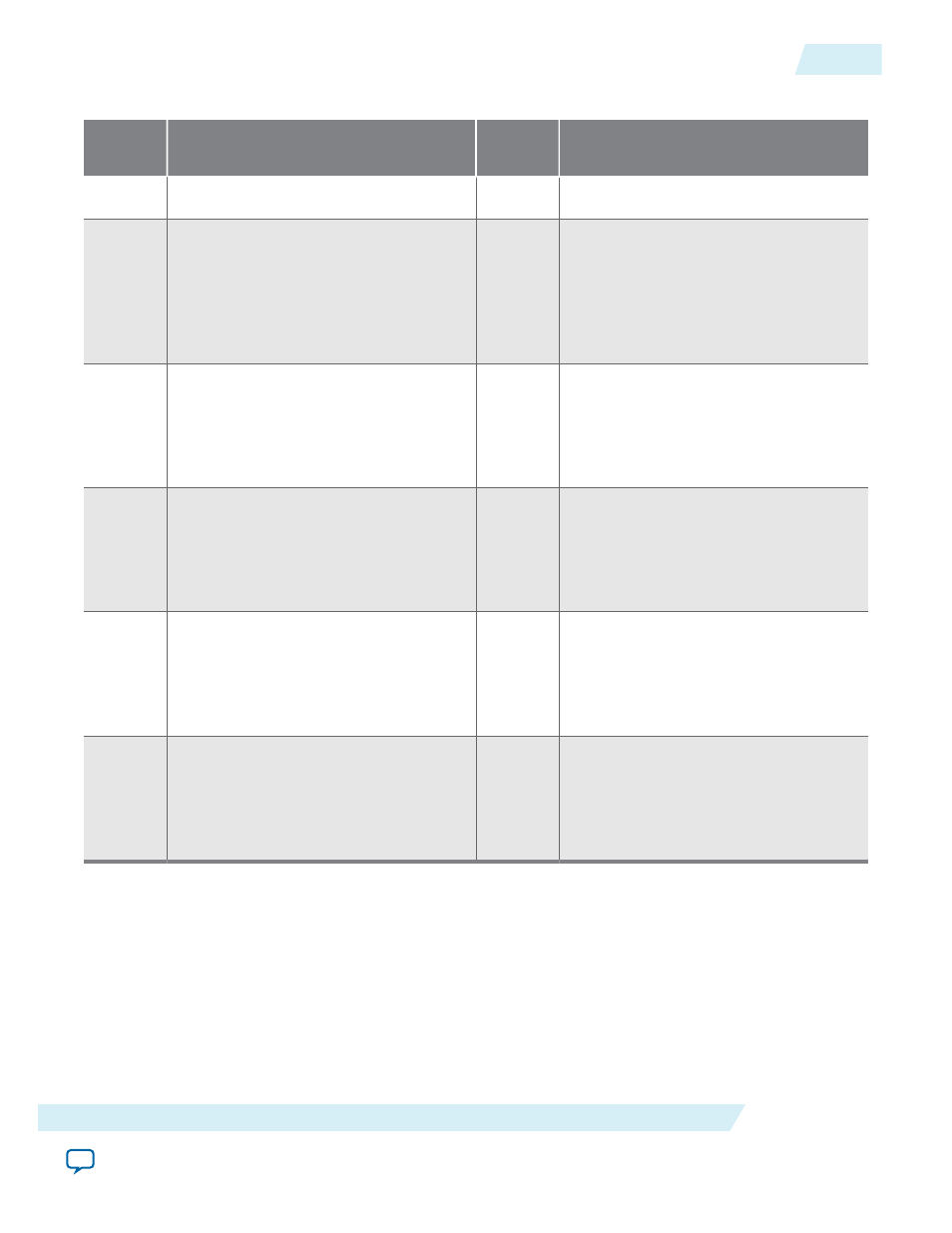

Table 6-25: INT‑X Interrupt Enable Register for Root Ports, 0x3070

Bit

Name

Access

Mode

Description

[31:5] Reserved

—

—

[4]

RPRX_CPL_RECEIVED

RW

When set to 1’b1, enables the assertion

of

CraIrq_o

when the Root Port

Interrupt Status register

RPRX_CPL_

RECEIVED

bit indicates it has received a

Completion for a Non-Posted request

from the TLP Direct channel.

[3]

INTD_RECEIVED_ENA

RW

When set to 1’b1, enables the assertion

of

CraIrq_o

when the Root Port

Interrupt Status register

INTD_

RECEIVED

bit indicates it has received

INTD.

[2]

INTC_RECEIVED_ENA

RW

When set to 1’b1, enables the assertion

of

CraIrq_o

when the Root Port

Interrupt Status register

INTC_

RECEIVED

bit indicates it has received

INTC.

[1]

INTB_RECEIVED_ENA

RW

When set to 1’b1, enables the assertion

of

CraIrq_o

when the Root Port

Interrupt Status register

INTB_

RECEIVED

bit indicates it has received

INTB.

[0]

INTA_RECEIVED_ENA

RW

When set to 1’b1, enables the assertion

of

CraIrq_o

when the Root Port

Interrupt Status register

INTA_

RECEIVED

bit indicates it has received

INTA.

Root Port TLP Data Registers

The TLP data registers provide a mechanism for the Application Layer to specify data that the Root Port

uses to construct Configuration TLPs, I/O TLPs, and single dword Memory Reads and Write requests.

The Root Port then drives the TLPs on the TLP Direct Channel to access the Configuration Space, I/O

space, or Endpoint memory.

UG-01145_avmm

2015.05.14

Root Port TLP Data Registers

6-29

Registers

Altera Corporation