Rx avalon-mm master signals, Rx avalon-mm master signals -3 – Altera Arria 10 Avalon-MM User Manual

Page 50

32-Bit Non-Bursting Avalon-MM Control Register Access (CRA) Slave

Signals

The optional CRA port for the full-featured IP core allows upstream PCI Express devices and external

Avalon-MM masters to access internal control and status registers.

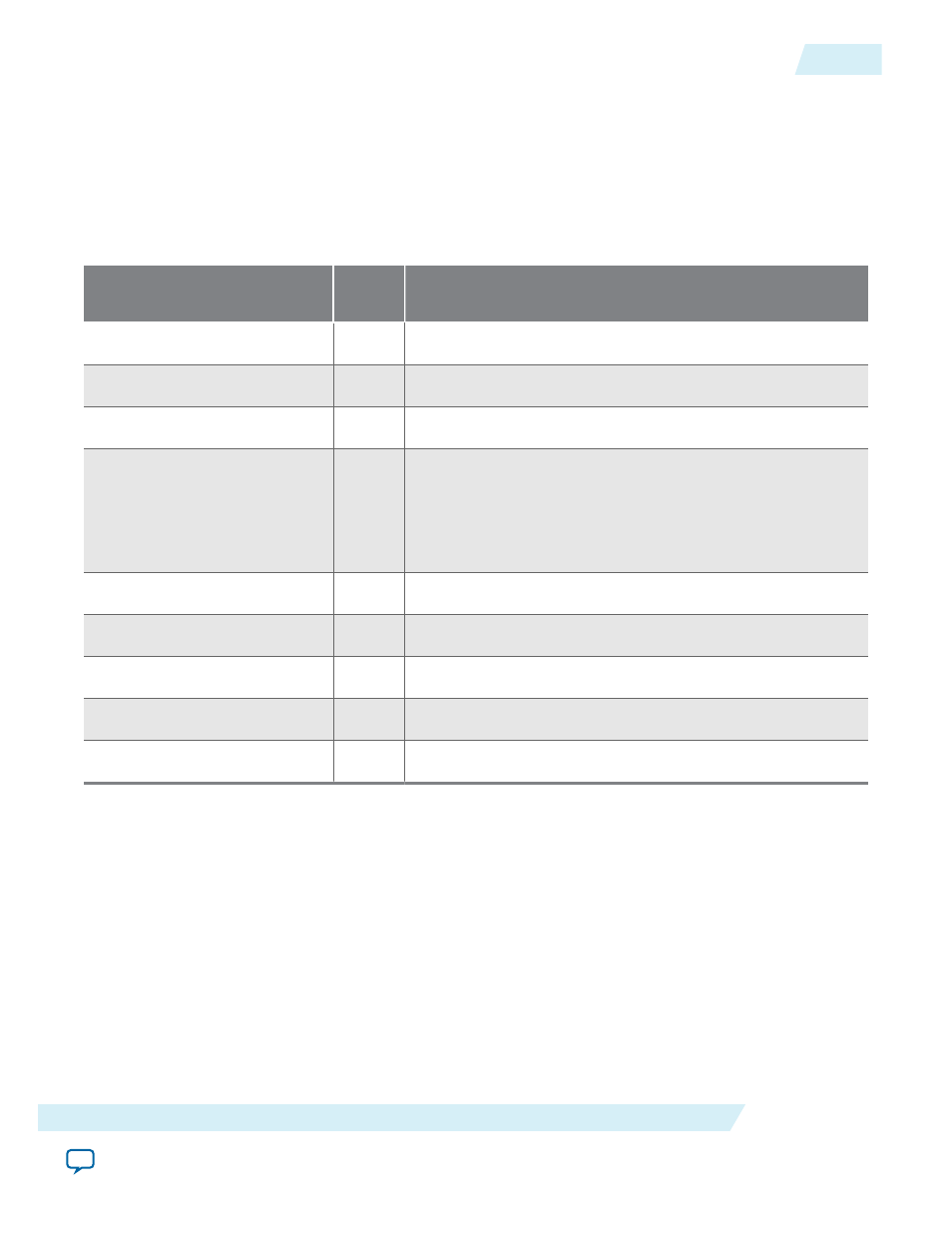

Table 5-1: Avalon-MM CRA Slave Interface Signals

Signal Name

Directio

n

Description

CraIrq_o

Output Interrupt request. A port request for an Avalon-MM interrupt.

CraReadData_o[31:0]

Output Read data lines

CraWaitRequest_o

Output Wait request to hold off more requests

CraAddress_i[13:0]

Input An address space of 16,384 bytes is allocated for the control

registers. Avalon-MM slave addresses provide address

resolution down to the width of the slave data bus. Because all

addresses are byte addresses, this address logically goes down

to bit 2. Bits 1 and 0 are 0.

CraByteEnable_i[3:0]

Input Byte enable

CraChipSelect_i

Input Chip select signal to this slave

CraRead_i

Input Read enable

CraWrite_i

Input Write request

CraWriteData_i[31:0]

Input Write data

RX Avalon-MM Master Signals

This Avalon-MM master port propagates PCI Express requests to the Qsys interconnect fabric. For the

full-feature IP core it propagates requests as bursting reads or writes. A separate Avalon-MM master port

corresponds to each BAR.

UG-01145_avmm

2015.05.14

32-Bit Non-Bursting Avalon-MM Control Register Access (CRA) Slave...

5-3

64- or 128-Bit Avalon-MM Interface to the Application Layer

Altera Corporation