Altera Arria 10 Avalon-MM User Manual

Page 209

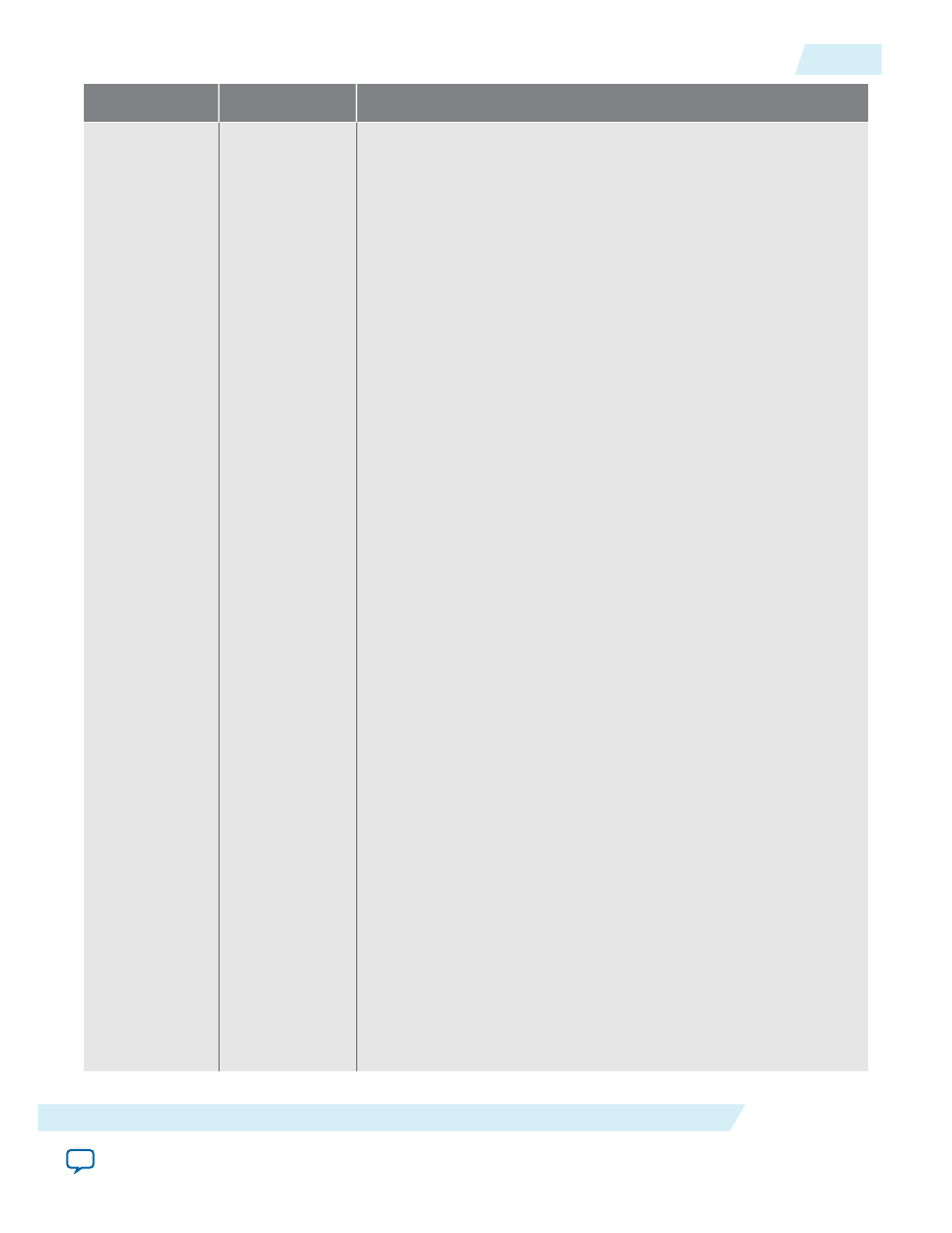

Date

Version

Changes Made

• Added simulation support for Phase 2 and Phase 3 equalization

when requested by third-party BFM.

• Added restrictions on the legal patterns of enabled and disabled

bytes for

txs_byteenable[

.

• Changed the PIPE interface to 32 bits for all data rates. This

change requires you to recompile your 13.1 variant in 14.0.

Made the following changes to the user guide:

• Changed device part number for Getting Started chapter to

10AX115R2F40I2LG.

• Corrected frequency range for

hip_reconfig_clk

. It should be

100-125 MHz.

• Clarified the behavior of the

txs_waitrequest

signal.

• Added statement that the bottom left hard IP block includes the

CvP functionality for flip chip packages. For other package types,

the CvP functionality is in the bottom right block.

• Simplified the Getting Started chapter. It copies the example from

the install directory and does not include step-by-step instructions

to recreate the design.

• Removed 125 MHz clock as optional

refclk

frequency in Arria

10 devices. Arria 10 devices support an 100 MHz reference clock

as specified by the PCI Express Base Specification, Rev 3.0.

• Added definitions for

test_in[2]

,

test_in[6]

and

test_in[7]

.

• Clarified that the Avalon-MM Bridge does not generate out-of-

order Avalon-MM-to-PCI Express Read Completions even to

different BARs.

• Added sections on making analog QSF and pin assignments.

• Enhanced the definition of Device ID and Sub-system Vendor ID

to say that these registers are only valid in the Type 0 (Endpoint)

Configuration Space.

• Updated Power Supply Voltage Requirements table.

• Removed all references to the Avalon-MM interrupt vector

register. This register is not used.

• Corrected values for Maximum payload size parameter. The sizes

available are 128 or 256 bytes.

• Removed

txdatavalid0

signal from the PIPE interface. This

signal is not available.

• Updated Power Supply Voltage Requirements table.

• Updated Physical Placement of the Arria 10 Hard IP for PCIe IP

and Channels to show GT devices instead of GX devices.

• Corrected bit definitions for

CvP Status

register.

• Updated definition of

CVP_NUMCLKS

in the

CvP Mode Control

register.

UG-01145_avmm

2015.05.14

Revision History for the Avalon-MM Interface

C-3

Additional Information

Altera Corporation