Altera Arria 10 Avalon-MM User Manual

Page 63

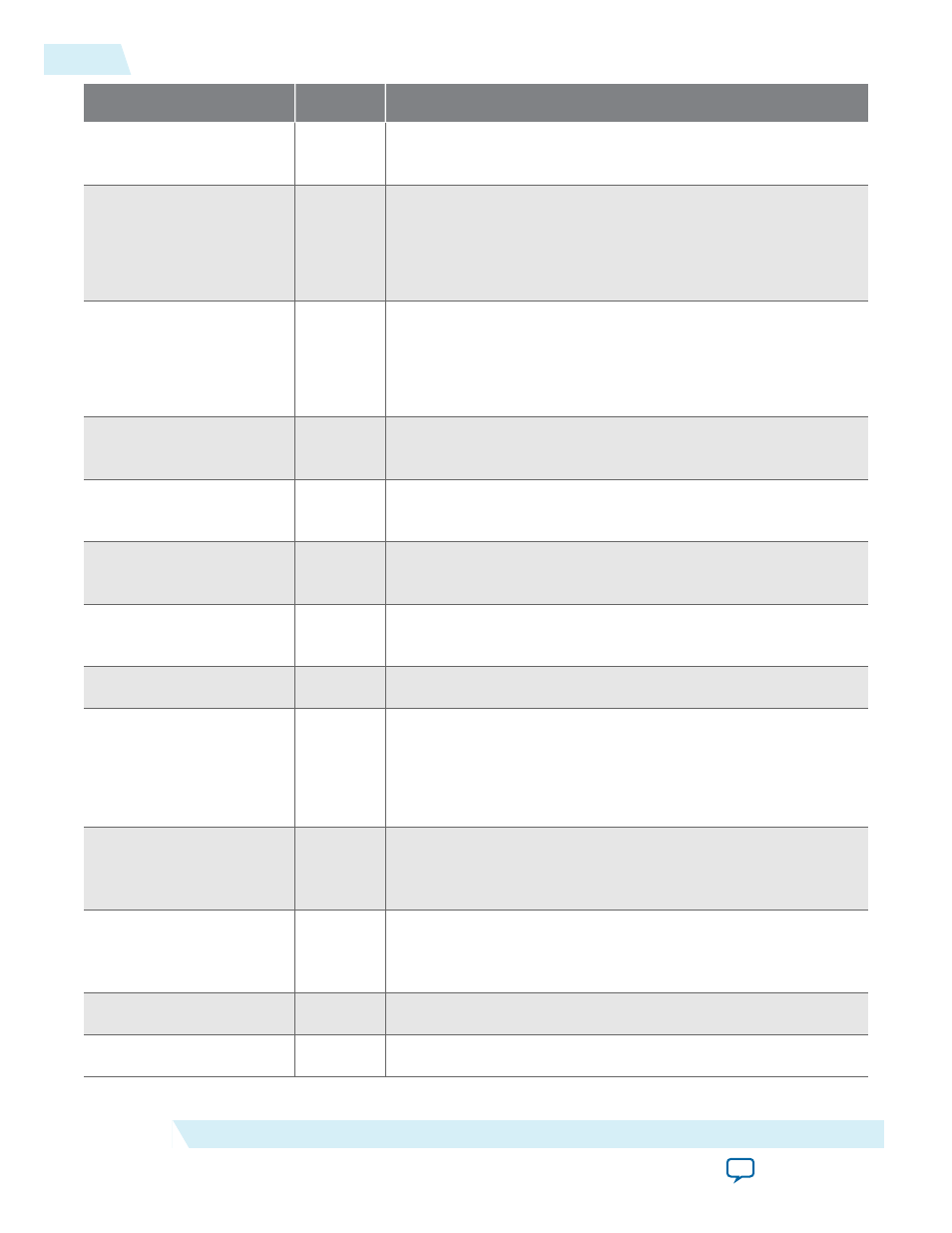

Signal

Direction

Description

txswing

Output

When asserted, indicates full swing for the transmitter voltage.

When deasserted indicates half swing.

txsynchd0[1:0]

Output

For Gen3 operation, specifies the transmit block type. The

following encodings are defined:

• 2'b01: Ordered Set Block

• 2'b10: Data Block

rxsynchd0[1:0]

Input

For Gen3 operation, specifies the receive block type. The

following encodings are defined:

• 2'b01: Ordered Set Block

• 2'b10: Data Block

rxvalid0

(1)

Input

Receive valid

data on

rxdata

rxdatak

phystatus0

(1)

Input

PHY status

PHY requests.

rxelecidle0

(1)

Input

Receive electrical idle

an electrical idle.

rxstatus0[2:0]

(1)

Input

Receive status

error codes for the receive data stream and receiver detection.

simu_mode_pipe

Input

When set to 1, the PIPE interface is in simulation mode.

sim_pipe_rate[1:0]

Output

The 2-bit encodings have the following meanings:

• 2’b00: Gen1 rate (2.5 Gbps)

• 2’b01: Gen2 rate (5.0 Gbps)

• 2’b1X: Gen3 rate (8.0 Gbps)

sim_pipe_pclk_in

Input

This clock is used for PIPE simulation only, and is derived from

the

refclk

. It is the PIPE interface clock used for PIPE mode

simulation.

sim_pipe_pclk_out

Output

TX datapath clock to the BFM PHY.

pclk_out

is derived from

refclk and provides the source synchronous clock for TX data

from the PHY.

sim_pipe_clk250_out

Output

Used to generate

pclk

.

sim_pipe_clk500_out

Output

Used to generate

pclk

.

5-16

PIPE Interface Signals

UG-01145_avmm

2015.05.14

Altera Corporation

64- or 128-Bit Avalon-MM Interface to the Application Layer