Faster system clock, Improved performance for arithmetic operations, User programmable interrupts – Echelon Mini FX User Manual

Page 17: User-programmable interrupts

4

Introduction

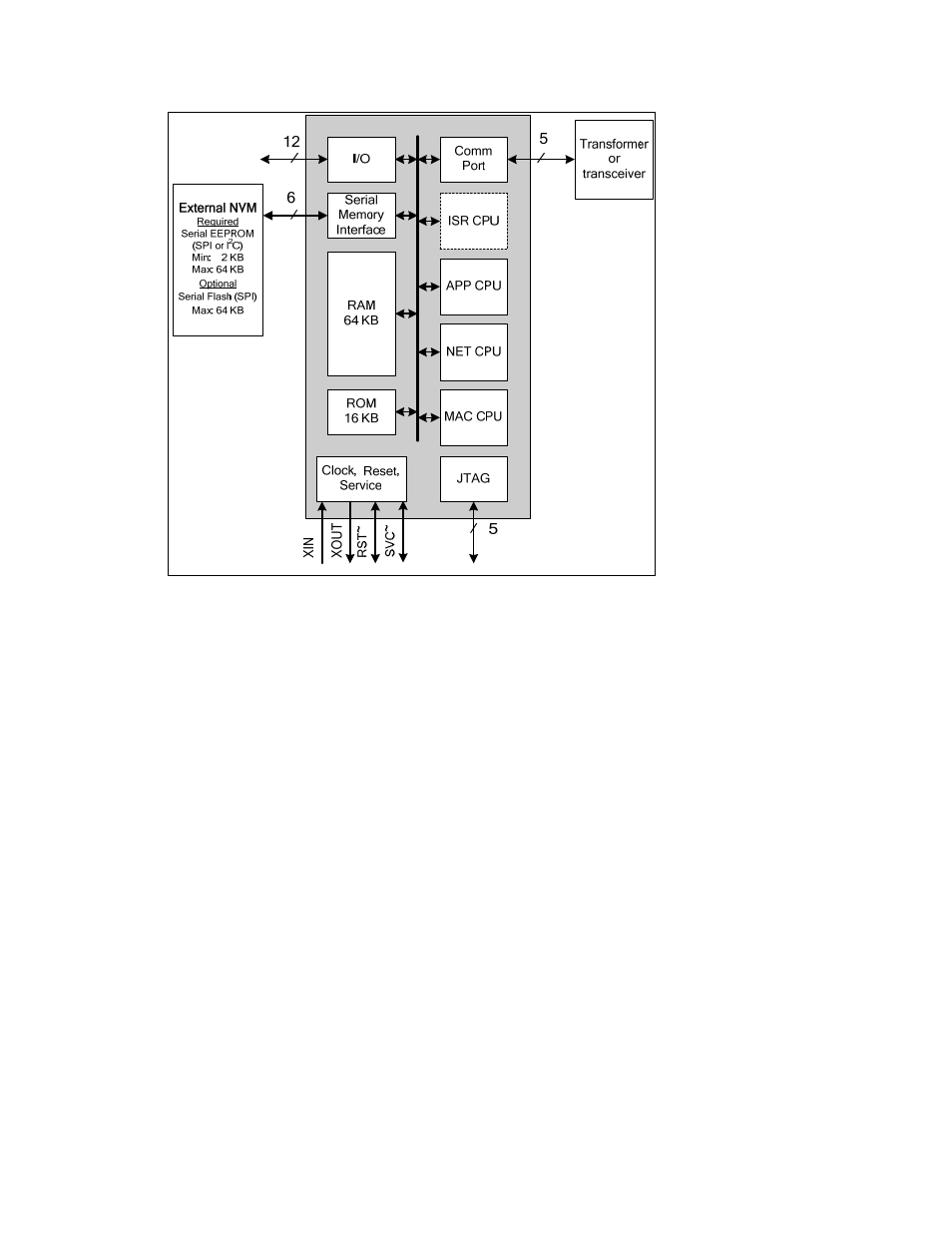

Figure 1.1 Series 5000 Chip Architecture

Faster System Clock

The Series 5000 chips support an internal system clock speed of up to 80 MHz (using an

external 10 MHz crystal). This results in application processing power that equals a

hypothetical FT 3150 Smart Transceiver operating at an external clock speed of 160MHz.

You can adjust the internal system clock speed from 5 MHz to 80 MHz through the

device’s hardware template. For more information on configuring the system clock of the

Series 5000 chips, see Appendix B, Creating and Editing Hardware Templates.

Improved Performance for Arithmetic Operations

The Series 5000 chips include 8-bit hardware multipliers and dividers, which are

supported by new Neuron assembly language instructions for multiplication and division.

These instructions use hardware multiply and divide functions to provide improved

performance for 8-bit multiplication and division. The older software multiplication and

division system functions are still supported, but many of these functions automatically

benefit from these faster hardware multipliers and dividers.

User-Programmable Interrupts

The Series 5000 chips let you define user interrupts that can handle asynchronous I/O

events, timer/counter events, and a dedicated, high-resolution system timer. A hardware

semaphore is supplied to help you control access to data that is shared between the

application (APP) and interrupt (ISR) processors on the Series 5000 chips.

At higher system clock rates (20 MHz or greater), these interrupts run in the dedicated

interrupt processor (ISR) on the chip. This improves the performance of the interrupt