Clock tree, Ipmc and cpld clocks, Major device clocks – ADLINK aTCA-N700 User Manual

Page 73: Figure 11-1 ipmc and cpld clocks

aTCA-N700 HW Users Guide

73

11. Clock

Tree

This section summarizes the clock tree of the board. Since there are no global synchronous operation

requirements, the ATCA backplane sync clock interface (CLK1, 2 and 3) are not present on the blade.

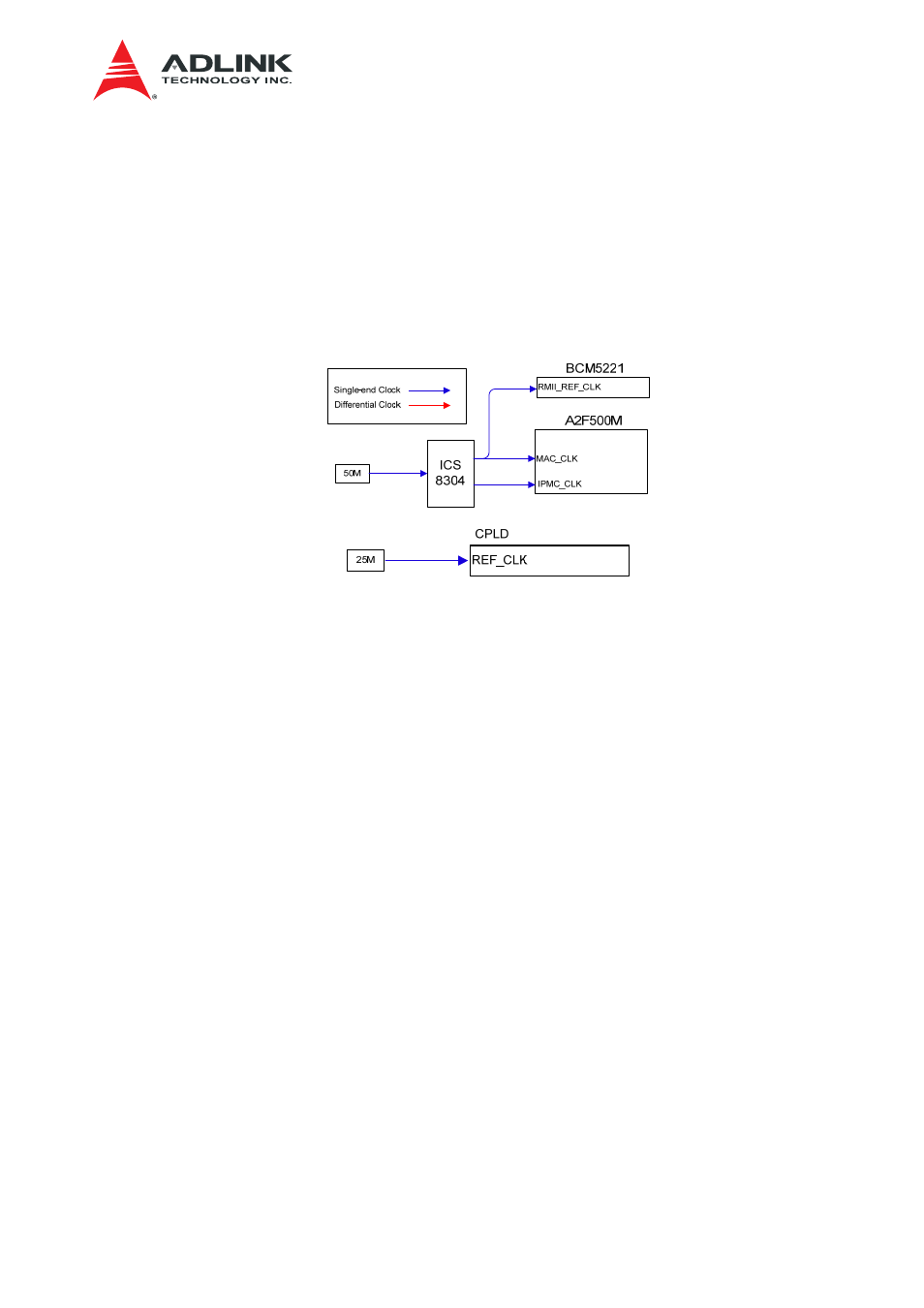

11.1. IPMC and CPLD Clocks

The IPMC, and the CPLD are control domain devices, which are independent from the data plane.

The clocks for these devices are shown in Figure 11-1.

Figure 11-1 IPMC and CPLD Clocks

11.2. Major Device Clocks

The data plane devices require reference clocks to drive SerDes signals. Since there is no need for

global synchronous operation on the SerDes ports, each device may get their own clock references

according to the device clock requirements. Three ICS85104 clock buffers are used for the 10G

SerDes interface references. Figure 11-2 illustrates the clock distributions for the major devices, used

for the data plane signals. All the PCI-e clock references come from a single source, ICS557-05, and

are distributed to four different devices, two CN6880s, the LMP, and the BCM56842.