Host interface, Figure 6-8 host interface – pcie, Figure 6-9 host interface - ethernet – ADLINK aTCA-N700 User Manual

Page 30

aTCA-N700 HW Users Guide

30

The mezzanine connectors should be able to pass 6.25Gbps Interlaken-LA signals at

sustainable quality. The MICTOR 1-1658016-2, 80 position connector as shown in Figure 6-7

is used. 12V supply voltage is fed to the mezzanine board with sufficient number of pins in

the connector (signals require 32pins, and the rest are for power and GNDs).

6.6. Host Interface

The CN6880 is capable of providing a 4 lanes @5Gbps PCI-e interface, but due to limitation

on the LMP, between the LMP and each CN6880, a 1x @2.5Gbps PCIe interface is provided

on the board as can be seen in Figure 6-8. The PCIe interface is used for configuration and

management of the CN6880. It could also be used for frame exchanges between the LMP

and the CN6880, with DMA enabled. All the PCI-e clocks to devices are from a single clock

buffer.

PCIe@1x

PCIe_CLK

SD[02]

P2041

BCM56842

PCIe

PCIe CLK

CN6880_A

PCIe CLK

CN6880_B

PCIe CLK

PCIe

PCIe

PCIe@1x

PCIe@2x

25

M_

XT

AL

IC

S557-0

5

SD[03]

SD[04/05]

Figure 6-8 Host Interface – PCIe

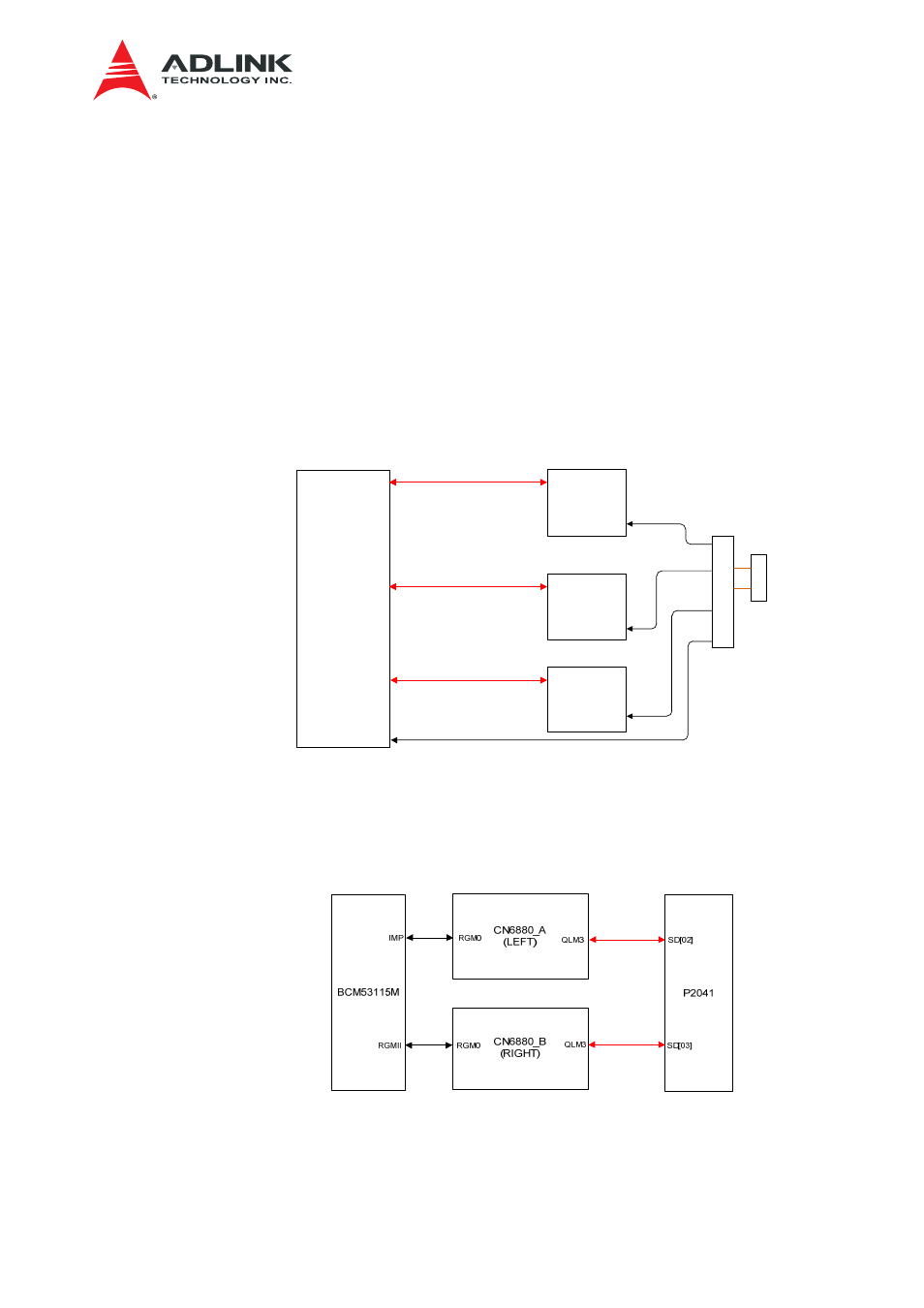

The management Ethernet ports from each NPU are connected to the Base Interface switch

as can be seen in Figure 6-9 via RGM0 interface. The base switch also provides a

connection to P2041 LMP, for the NPUs to connect to the LMP.

Figure 6-9 Host Interface - Ethernet