Clock, Other interfaces, Mdc/mdio: miim – ADLINK aTCA-N700 User Manual

Page 37: Bsc (i2c) interface, Led control, Figure 7-3 switch led_data0 format

aTCA-N700 HW Users Guide

37

7.5. Clock

There are six Trident input clocks:

•

Four SerDes reference clocks: CML clocks at 156.25MHz. One clock per Warp

Core group. XG_PLL[3:0].

•

PCIe reference clock: 100MHz differential.

•

Core clock: 25MHz CML.

The Trident switch runs in a self running mode without backplane sync clocks.

The Trident provides the two reference clocks RECOV_CLK_0/1 recovered from its

SerDes ports for any global sync purpose, which is now unused. The board level clock

tree is described in Section 11.

7.6. Other Interfaces

7.6.1. MDC/MDIO: MIIM

The Trident contains one CPU Management Interface Controller ((CMIC) supporting

IEEE 802.3u standard MII management (MIIM) interface, so called MDC/MDIO interface.

The MDIO interface allows the P2041 LMP to access MDIO devices through the switch.

Such MDIO devices include the RTM PHY devices. The strapping for the MDIO_22_SEL

is set to HIGH (1: 2.5V or 3.3V, 0: 1.2V) to set the MDIO signal level.

7.6.2. BSC (I2C) Interface

The Trident switch provides a Broadcom Serial Control (BSC) interface to communicate

with other devices in I2C compatible format. The signals for the interface are BSC_SCL,

BSC_SDA, BSC_SA0, and BSC_SA1. The operation mode is controlled by BSC_MODE

and is set to be 0. (0: BSC Master, 1: PCI I/F used and BSC Master)

On the blade, however, these signals are not used and left N.C.

7.6.3. LED Control

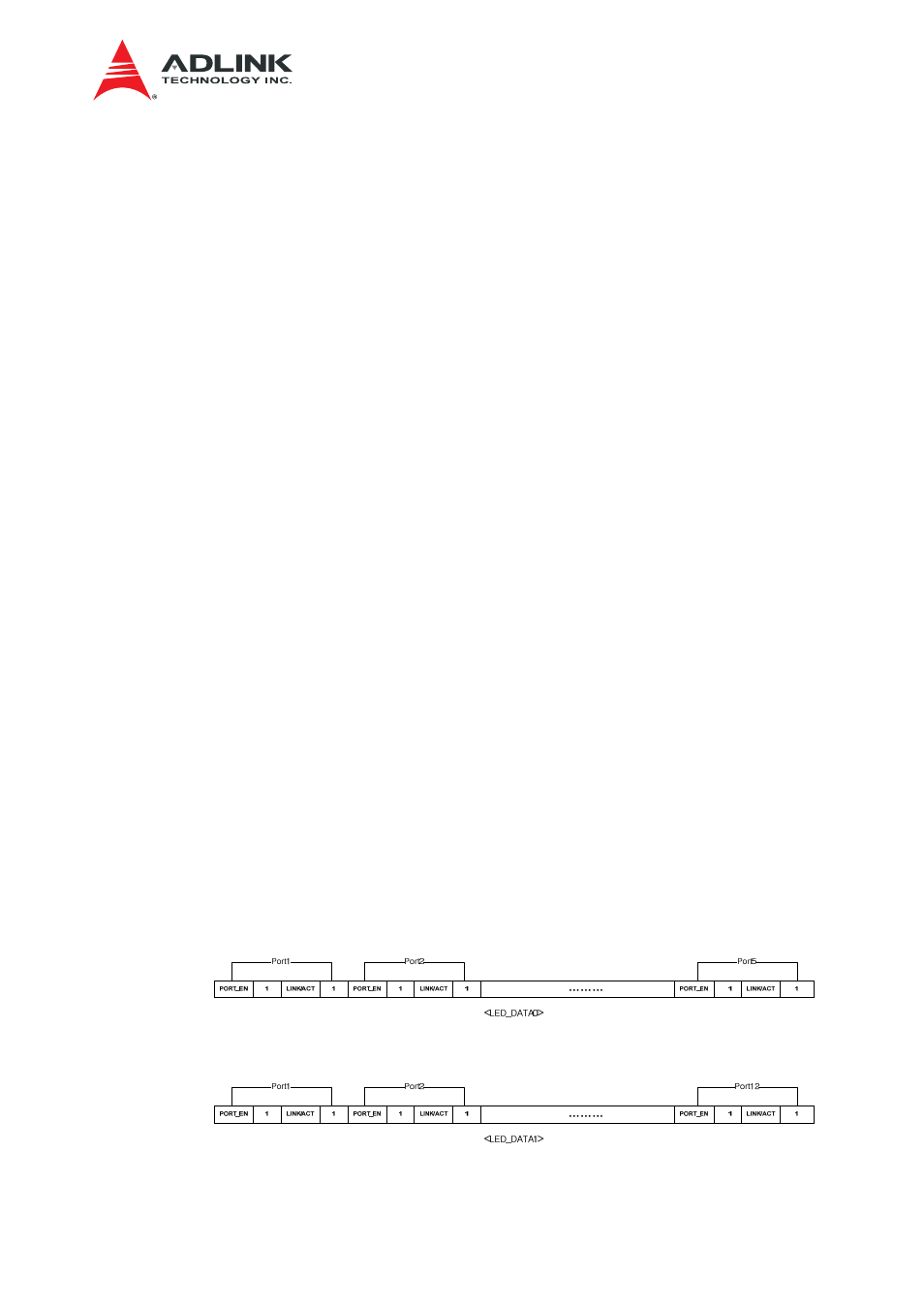

The LED interface consists of four signals: LED_CLK[1:0], LED_DATA [1:0].

These signals are used to send out the LED control signals based on MAC status data

over the time multiplexed data pins. The LED_CLK operates at 5MHz. LED_DATA[0]

contains the information for Serdes[36:1] and LED_DATA[1] for Serdes[72:37].

DATA[0] format is in 40bits and DATA[1] is in 80bit as shown in Figure 7-3. On the

board, DATA[1] is being used as described in Table 7-3.

Figure 7-3 Switch LED_DATA0 Format

- LED_DATA1 format(80bit)

Figure 7-4 Switch LED_DATA1 Format