Interrupts, Table 8-2 p2041 interrupt signal connections – ADLINK aTCA-N700 User Manual

Page 47

aTCA-N700 HW Users Guide

47

The MUX selection enables to select one of the two destinations of the UART #1

port and controlled by the P2041. Some selected UART features include:

• Full-duplex

operation.

• Programming model compatible with original PCI16450 UART and PC16550D

(Improved version of PC16450 that also operates in FIFO mode).

• FIFO mode for both transmitter and receiver, providing 16-byte FIFOs.

• Line-break

detection and generation.

• Internal diagnostic support, local loopback, and break functions.

The UART_1 pin out of the serial interface RJ-45 connector is compliant to Cisco pin

out as can be seen in Table 3-1 and Table 3-2.

8.1.6. Interrupts

The P2041 has an internal Programmable Interrupt Controller (PIC) which handles

various external and internal interrupts connected to the pins. All the interrupt sources

and their handlings are found in the P2041 datasheet and some are summarized as:

• IRQ[0:11] Signal support

• Interrupts generated from within the PIC itself, which are as follows:

-

Global timers A and B internal to the PIC

- Inter-Processor

Interrupts(IPI)

- Message

registers

-

Shared message signaled registers

• Three types of programmable interrupt outputs:

-

External Interrupt : int0, int1

-

Critical Interrupt : cint0, cint1

- IRQ_OUT#

• Programming model compliant with the OpenPIC architecture

• Support for two processors

• Processor core initialization control

• Programmable resetting of the PIC through the global configuration register

• Pass-through mode(PIC disable) in which the PIC directs interrupts off-chip for

external servicing

The external interrupt signals are routed as the following table.

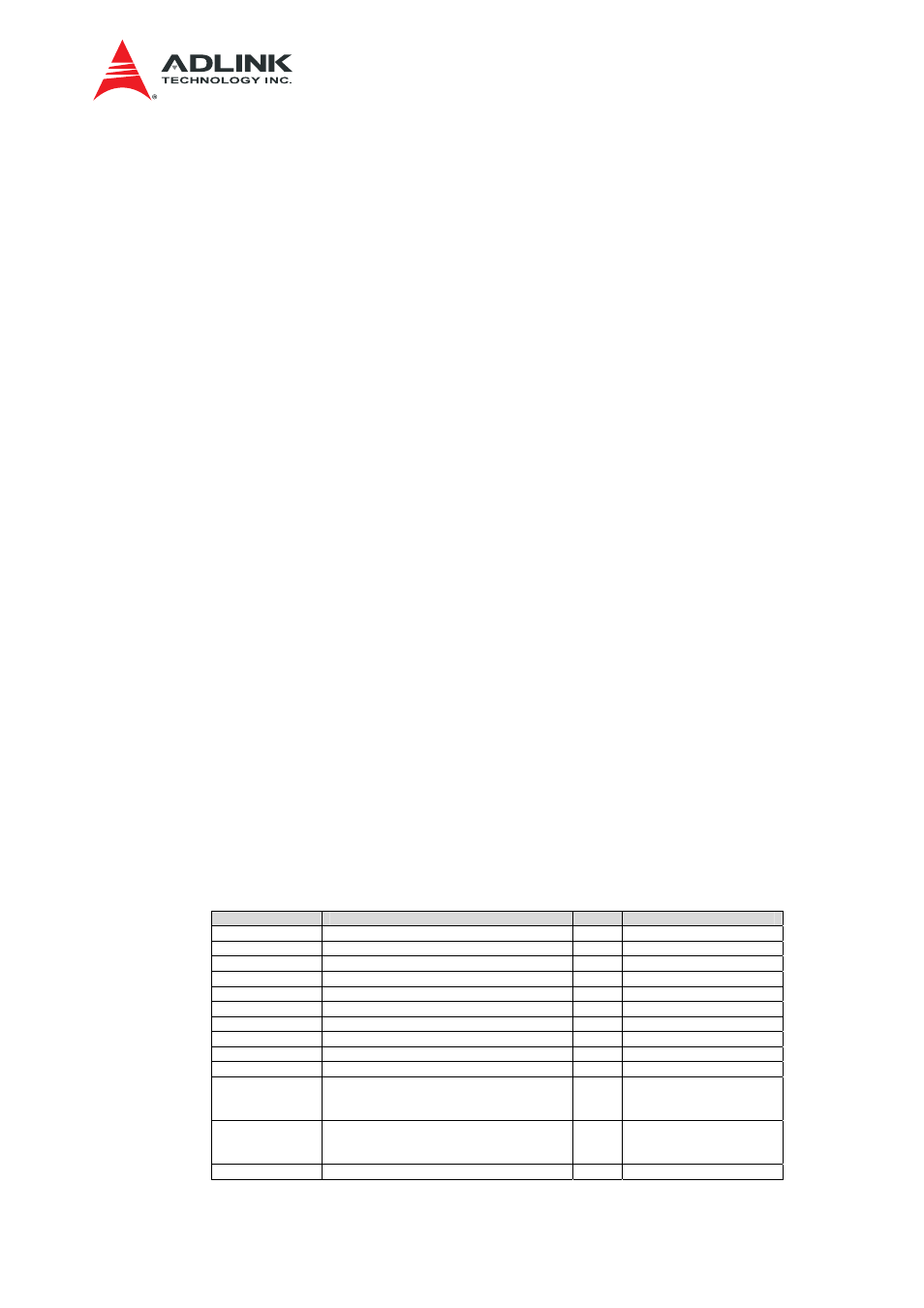

Table 8-2 P2041 Interrupt Signal Connections

Pin Name

Connection

I/O

Description

IRQ0

Connected to CPLD

-

Reserved

IRQ1

BCM53115M Interrupt pin

I

IRQ2

SYS CPLD Interrupt pin

I

IRQ3/GPIO[21]

CPLD Interrupt for SFP information

I

IRQ4/GPIO[22]

Connected to CPLD

I

IRQ5/GPIO[23] RTM

Interrupt

pin

I

IRQ6/GPIO[24]

Connected to CPLD

-

Reserved

IRQ7/GPIO[25]

Connected to CPLD

-

Reserved

IRQ8/GPIO[26]

USB1_DRVVBUS

O

USB Power Enable

IRQ9/GPIO[27]

USB1_PWRFAULT

I

USB Power fault alarm

IRQ10/GPIO[28]

RTM RESET

O

RTM RESET

0 : RESET

1 : Normal

IRQ11/GPIO[29]

BOOT FLASH Selection of IPMC

I

BOOT Flash select

0 : Master flash

1 : Slave flash

IRQ_OUT# Interrupt

output

O